4 乘法器的FPGA实现和仿真

在顶层乘法器WALLACE TREE逻辑架构设计中,可以通过描述语言模块例化来调用前面手动实现的6:4压缩器,可将slICe压缩模块看成一个FPGA中固有的IP硬宏模块,调用方法与使用FPGA器件内部的其他IP没有区别。在FPGA Editer中对各个模块相互位置按树的层次和数字逻辑顺序进行约束排列,形成一个约束文件。这样FPGA芯片面积资源不仅得到充分的利用,在时序方面也会减小关键路径的时延,提高时钟频率。

该乘法器的末级加法器要把WALLACE TREE得到的最后2个部分积快速的相加得到最终结果。末级加法器的实现方法有CPA(Carry Propaga tion Adder),该加法器的利用超前进位,可以使进位链这个关键路径的时序在逻辑上层次减小。但该加法器在FPGA综合实现后形成复杂结构,带来的是利用了很大的布局面积和布线资源。FPGA内部结构中以其特有纵向结构的超级进位链,可将进位的器件延时和布线延时优化。可以利用该进位链,合理进行布局约束优化,使进位链路径时序减小。实践表明,在16×16的加法器中,该进位链的时延只有6 ns左右,大大减小了整个乘法器关键路径延时。在图4中列出了本设计的FPGA布局布线布局布线后仿真结果。该结果在XILINX-Virtex5-VC5VSX35T器件中运行,通过ModelSim仿真输出采集。multin_a和multin_b分别是16位乘数,aCC_out是相乘后输出的32位结果,rst_n是复位清0信号。整个设计的硬件描述语言采用Verelog语言,其中例化了预先用FPGA Editer工具设计好的6:4硬宏压缩模块。

图5给出了WALLACE TREE乘法器设计的XILLNX-Virtex5-VC5VSX35T器件实际运行性能参数。该结果是FPGA器件以系统时钟为120 MHz运行时,通过XILLNX公司ISE套装软件ChipScope采集获取的数据。图中,unt1和unt2采用FPGA内部一个测试计数器输出的16位无符号乘数,将其输入WALLACE TREE乘法器运算后,得到一组32位乘积结果。该实测结果表明,该结构的乘法器能工作正常工作在120 MHz系统时钟的条件下,其实现电路关键路径的延时小于8.33ns。

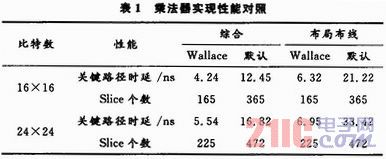

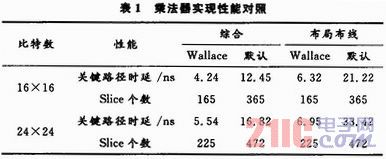

表1分别列出了16×16,24×24位乘法器在FPGA中用工具默认方法和本文方法生成的资源和时序对照图。可以看出,本文的结构更合理,资源和速度都得到了一定程度的优化。

5 结语

本文根据FPGA内部标准单元结构,提出了一种改进的WALLACE TREE 6:4压缩器的新型逻辑结构,并用Xilinx提供的工具套件FPGA Edi-ter实现了该压缩器单元。结合乘法器在FPGA中的仿真表明,该结构的乘法器在提高系统的时钟频率和节省布局布线方面都有很大的优势。

上一页 [1] [2] [3]