摘要:为了使基于FPGA设计的信号处理系统具有更高运行速度和具有更优化的电路版图布局布线,提出了一种适用于FPGA结构的改进型WALLACE TREE架构乘法器。首先讨论了基于标准单元3:2压缩器的改进型6:4压缩器,根据FPGA中slICe的结构特点通过在FPGA Editer软件工具编辑,对该压缩器进行逻辑优化,将其应用于FPGA的基本单元slice结构中。并对乘法器的其他部分结构优化整合,实现一个资源和性能达到合理平衡,且易于在FPGA中实现的乘法器。实际运行结果表明,该乘法器的关键路径延时小于8.4 ns,使乘法器时钟频率和系统性能都得到很大提高。

关键词:乘法器;WALLACE;FPGA;6:4压缩器

在数字信号处理中,乘法器是整个硬件电路时序的关键路径。速度和面积的优化是乘法器设计过程的两个主要考虑因素。由于现代可编程逻辑芯片FPGA的集成度越来越高,及其相对于ASIC设计难度较低和产品设计周期短,受到很多厂家和研究机构的关注。利用它的可编程和可扩展性,可将传统乘法器设计方法应用到FPGA芯片中。乘法器设计基本上是部分积的生成及其之间的相加的优化过程。针对FPGA内部固有结构的特点,本文着重介绍了一种基于WALLACETREE优化算法的改进型乘法器架构。根据FPGA内部标准独特slice单元,有必要对WALLACE TREE部分单元加以研究优化,从而让在FPGA的乘法器设计中的关键路径时延得以减小,整体时钟性能得以提高。也能够使FPGA的面积资源合理优化,提高器件的整体资源利用率。

1 WALLACE TREE结构

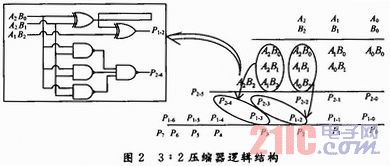

WALLACE TREE是对部分积规约,减小乘法器关键路径时延的一种算法。传统WALLACE TREE结构的CSA(Carry Save Adder)阵列乘法器如图1所示,其中“·”代表生成的多个部分乘积项,相应电路中用逻辑与门来实现。求和阵列将前面生成的多个部分积通过3:2 CSA压缩器,将其压缩成2个部分积,最后通过末级进位相加得到所需的最终乘积结果。图中矩形框所示为3:2 CSA压缩器,其电路逻辑等效于一个全加器结构。通过运算可知N个部分积,要经类似的log(2N/3)级3:2压缩,就可得到2个部分积。

2 压缩器的优化

由于FPGA内部的结构是固定的,没有以上WALLACE TREE所需要的CSA标准全加器结构。因此,在传统的FPGA电路综合实现时,该CSA全加

器被综合在FPGA内部查找表(LUT)和进位链中,占用了整个slice单元的资源。由于经典WALLACETREE结构不具有良好的对称性且需要权重对齐等因素,势必要增大FPGA电路的复杂度,增加大量的FPGA内部布局和布线资源,在FPGA中不规则的布局布线结构,也增大了关键路径的时延。

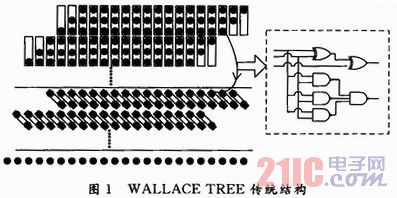

为在FPGA中较好地实现WALLACE TREE结构,结合FPGA中最小标准单元的结构SILce,对CSA全加器单元结构加以改进。如图2所示,可将WALLACE TREE相邻的平级3:2 CSA压缩器合并成一个6:4压缩器。该压缩器只需使用1个FPGA的silce资源,就能实现其数字逻辑。下面以3×3乘法器为例,进行WALLACE TREE压缩器的推导和优化。如图2的第一个部分积,部分积低位空白应补0,高位空白位用该部分积的最高位补齐。