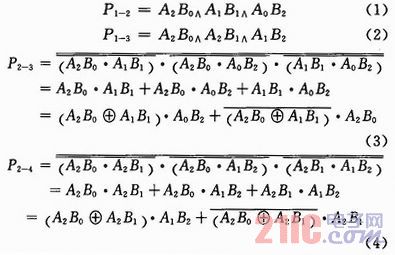

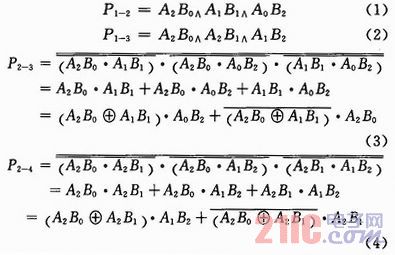

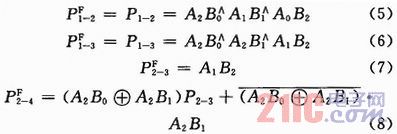

下面对2个3:2 CSA压缩器合并成一个6:4压缩器单元运算逻辑做理论推导,其中:

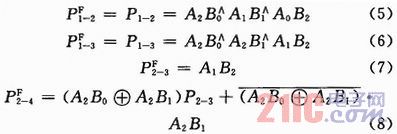

合并这两项3:2压缩为6:4压缩时,A1B2和P23属同级进位,在计算过程中可将这两项的位置互换,因此上式可推导演化成:

3 改进CSA的FPGA实现

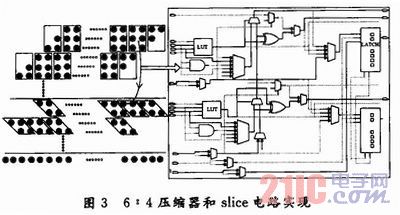

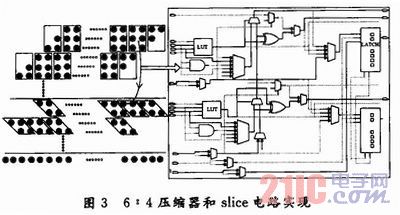

Xilinx提供了一项强大的用户界面软件工具FPGA Editer,可以通过手动编辑和修改FPGA最基本的标准单元slICe结构,使其符合所需要的逻辑。图3左边是一个WALLACE TREE 6:4压缩的整体结构,右边是实现架构中一个6:4压缩的FPGA内部标准单元slice。slice电路中虚线是器件原有的预布线,实线是根据实际电路逻辑手动编辑后slice内部电路布线。根据上一面的推导式(5)~(8),slice内部的2个查找表(LUT)单元被配置成2输入异或门单元。为了使整体WALLACE TREE布线齐整,还将式(7)直通逻辑实现也在该级slice压缩器中完成,其中输入电平A1B2经过2个MUX和一个配置为1的常有效LATCH输出到

/2011.08/13/i.jpg)

,形成一个直通电路。

从图3可以看出,WALLACE TREE的6:4压缩器单元只用一个slice就可以实现。而几乎所有Xilinx的FPGA器件内部slice结构都类似,因此该6:4压缩器在基本的FPGA器件中都可以通过此手动编辑方法实现,形成一个可供顶层WALLACETREE逻辑调用的硬宏模块。

上一页 [1] [2] [3] 下一页