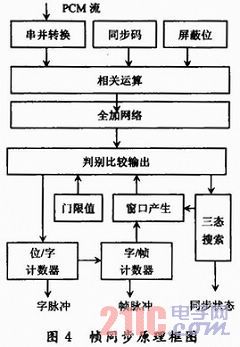

PCM数据按时钟进行串/并转换,与本地帧同步码进行同或运算后再与上屏蔽位,由全加网络将相关运算结果按位相加统计结果中1的个数,大于门限值则表示可能接收到了帧同步码。

为避免虚警和漏检,使帧同步器稳定可靠工作,采用搜索、校核、锁定三态逻辑。

系统开始时处于搜索态,符合相关器输出,由搜索态转入校核态。在预期检测窗口内没有帧码,从校核返回到搜索态。连续通过校核数α,进入锁定态。为避免帧同步码的漏检,连续漏检超过保护帧数β,帧同步才返回搜索态,否则保持在锁定态,帧脉冲由本地产生。

2.2 IRIG—B码解调

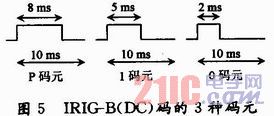

IRIG时间序列码是一种串行码,共有3种码元,如图5所示。

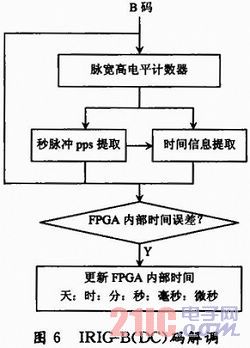

P码元是位置码元,连续2个P码为一帧的开始,第1个P码元定义为P0,第2个P码元为秒脉冲pps,上升沿为该秒的准时刻,时间信息以BCD码依次分布在其后的码元中。解调时先进行pps的提取,再进行秒、分、时、天的信息提取,其流程如图6所示。

时钟频率为1 MHz,用计数器对输入信号的脉宽进行计数。8 ms,5 ms,2 ms脉宽计数为8 000,5 000,2 000。输入B码的脉宽会混有干扰,晶振时钟也存在一定的误差,计数器的计时判别应浮动一个范围,设置门限为脉宽的85%~115%,当满足一定范围的数值时,分别输出P码,0码,1码信号。

FPGA中的时码产生“天:时:分:秒:毫秒:微秒”信息。解调出B码时,FPGA更新内部时间,B码中不含毫秒与微秒信息,由FPGA根据秒脉冲信息的准时刻来生成。

3 FPGA驱动程序开发

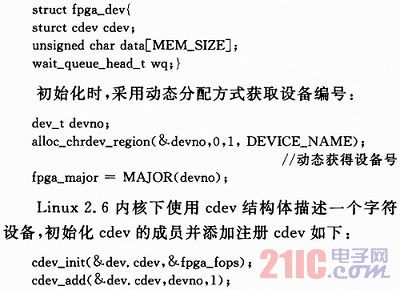

在Linux中,所有的硬件设备都像常规文件一样进行打开、关闭和读/写。把FPGA当作字符设备进行设计,驱动由设备加载与卸载,以及文件操作file_operation结构体中成员函数组成。

3.1 加载与卸栽设备驱动

FPGA设备驱动程序初始化流程为动态获得主设备号、字符设备注册和申请中断;卸载流程为注销设备,释放设备编号。

定义一个设备结构体来表示FPGA,如下: