简介:给出一种具有多种触发功能的可编程高速数据采集模块的设计方法。模块可以动态设置触发窗长度、触发点电平、触发极性和触发模式;依据触发字与存储在FIFO中的A/D转换数据比较确定触发位置,并根据设置的预触发深度实现对A/D转换数据的存储和传输。由于触发电路采用了全数字化设计,与采用模拟电平比较器实现触发电平比较相比,无需硬件改动,可以灵活地配置触发方式,同时也降低了系统调试难度。

关键词:高速数据采集;数字电路;触发窗;先进先出存储器

引言

在数据采集的过程中,为了不漏掉任何一个既定特征的信号,A/D转换器必须不断地采集数据。但是由于存储器容量的限制,不可能无限制地采集并存储数据。如何使模块能自动检测、采集并存储有效数据呢?触发技术的引入可以解决这一问题。触发是为了有效地观测信号,当被测信号满足触发条件时,启动一次数据采集,使用户在屏幕上能观测到满足触发条件的波形。

触发电路在以往的设计中,多采用电平比较器,其缺点是:采用的分立元件多,不利于模块移植和速度的提升,同时触发方式多样化配置也受到硬件限制,不具备智能化特点。本模块基于高速A/D转换器和FPGA,提出了一种全数字化的多种触发功能的高速数字采集设计方案。模块接口易于移植,采集频率高达50 MHz,具有多种可编程触发功能,采用的触发窗技术进一步保证了采样存储数据的正确性和有效性。

1 高速数据采集模块结构

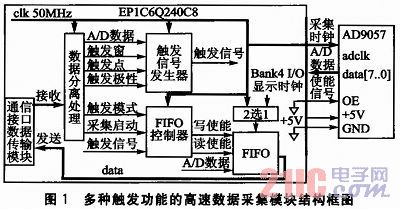

高速数据采集模块由FPGA存储控制、传输电路和AD9057数据采集部分构成。其中FPGA为此次模块设计的重点。多种触发功能的高速数据采集模块结构框图如图1所示。采用Cyclone系列EP1C6Q240C8型号的FPGA控制芯片,其Bank4 I/O口与AD9057相连,有源晶振提供了50 MHz的时钟频率。

此模块通过通信接口动态设置触发极性、触发模式、触发窗长度、触发点电平,触发极性可选上升沿触发rising_edge和下降沿触发falling_edge两种。触发模式可分为前触发pre_trigger、中间触发mid_trigger、后触发post_trigger三种模式。触发窗长度设置为0~100的整数,触发点电平可设置为0~255的整数。

当连接通信接口的外部显示控制界面设置好触发极性、触发模式、触发窗长度、触发点电平时,开始启动采集命令,包装好的40位数据流将被发送到FPGA;FPGA接收到40位数据后,迅速分离成5个8位数据,即触发极性、触发模式、触发窗长度、触发点电平和采集启动信号,利用FIFO存储器先进先出的特性以及对AD9057的控制时序,配合触发信号存储A/D数据;当采样完成后,FIFO中的数据可以被发送到外部的显示控制界面直观地显示出来。