摘要:提出了以AVR ATmega128单片机和ALTEra公司的Cyclone系列EP1C3T100为核心的系统设计方案。分析了数字式低频相位测量仪的测量原理和测量误差及其消除的方法。主要介绍了系统的软硬件设计。实践表明,此方案设计的相位仪对低频正弦波信号实现精确测频和测相位差,具有处理速度快、稳定可靠、精度高等优点。

关键词:数字相位仪;单片机;FPGA;误差;频率;相位差

本设计采用MCU和FPGA相结合的系统方案,以AVR单片机ATmega128和Altera公司的Cyclone系列EP1C3T100为核心,充分发挥各自的优势,如AVR单片机先进的RISC结构和强劲的运算、控制功能,Altera公司的FPGA运算速度快、资源丰富以及易编程的特点,合理设计,此方案的相位仪具备速度快、稳定可靠、精度高等优点,而且容易实现“智能化”和“自动化”。

1 系统方案设计

1.1 测量方法的比较与选择

目前相位测量的方法主要有两种:

1)DFT测相法即将待测信号通过A/D转换得到f(n),f(n)按离散傅里叶变换得出离散频谱F(k),f(n)和F(k)为傅里叶变换对,通过运算得到两路信号的基波相位,从而计算出相位差。DFT测相法的精度受限于ADC的采样精度,需要高速ADC对信号进行过采样,测量方案复杂,可以通过采集卡在计算机上实现虚拟仪器,所以主要应用在精度要求很高的场合和虚拟仪器中。

2)填充计数测相法 即两路同频的正弦信号经过信号整形电路后得到方波信号,方波信号经过鉴相器后,得到两路输入信号的相位差信号,用固定频率的采样脉冲进行填充并计数,从而计算出相位差。填充计数测相法主要应用在要求一定的精度,测量的频率不是太高但实时性要求很强的场合,易于实现数字化和自动化,低频数字相位仪适合用填充计数法。

填充计数测相法的基本算法:若正弦波整形后的方波信号频率为f,周期为T,采样脉冲周期为TC,方波一个周期内对采样脉冲计数为,n则被测信号频率f=1/T=1/NTC。同样的方法测出两个同频正弦波起点之间的时间差为△t,则两信号的相位差△θ=△t·360°/T。

1.2 系统方案的确定

由系统测量方法可知,数据需要采集、运算及显示,考虑到FiELD Programmable Gate Array(FPGA)集成度高、I/O资源丰富、稳定可靠,选择余地大,外围元件很少,近年来价格下降等优势,以及MCU良好的人机接口和运算控制功能,所以本系统由MCU和FPGA相结合构成测控主体。FPGA负责采集测频和测相位差的脉冲信号,MCU负责读FPGA采集的数据,计算待测信号频率和相位差并在LCD上显示。

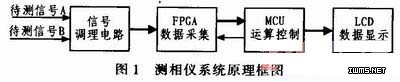

所以,系统由4个部分组成:待测信号调理电路、FPGA数据采集电路、MCU数据运算控制电路和LCD数据显示电路,如图1所示。

2 测量误差的分析与消除

相位测量仪的完善设计,不仅要有合适的测量方法和系统实现方案,还需要着重分析误差产生的原因和确定消除的方法。

1)填充时钟频率(即数据采样信号)的影响与确定本相位测量仪的测频范围为20 Hz~20 kHz,相位差的范围为△θ=0°~359.9°,相位差的显示分辨率为0.1°,要求测量相位的绝对误差≤2。

被测频率20 Hz≤f≤20 kHz,则周期50μs≤T≤50 ms。

T=50 μs,绝对误差取0.1°~2°。

则填充时钟信号周期:0.1°x50 μs/360°≤TC≤2°x50 μs/360°即:1/72(μs)≤TC≤1/3.6(μs),可以得出填充时钟频率:

3.6 MHz≤fC≤72 MHz。

T=50ms内对TC=1/3.6(μs)的填充脉冲计数,计数值Nmin=180000≤218;对TC=1/72(μs)的填充脉冲计数,计数值Nmax=3600000≤ 222。

本设计考虑MCU的计算及分频取得信号的方便,填充时钟信号频率fC=20 MHz,测量绝对误差<1°,FPGA在20 MHz时钟信号作用下对待测信号周期和相位对应的时间差进行计数,FPGA采样的二进制数据位为20 bit,可以保证测量的精度。

2)待测信号调理电路中零点漂移的影响与消除待测信号调理电路主要作用是把输入信号整形变换成矩形波,通常采用过零比较器或者施密特触发器。

过零比较器在零点电位附近可能会有振荡,输入信号在零点电位附近时,电压比较器处于放大区,整形后的矩形波在边沿会产生抖动,使系统无法进行测量。要消除这种抖动,可以采用施密特触发器。为了保证测量的精度,施密特触发器必须符合两个条件:一是两路被测信号幅度基本相等,二是门限电平要基本接近。

3)整形后方渡边沿的陡峭程度的影响与消除信号经过整形后输出的矩形脉冲信号直接送给FPGA,则FPGA不能立即获取稳定的数字脉冲信号,就会使系统的精度受到很大影响。这主要是由于整形后方波边沿不够陡峭造成的。要解决此问题,一是选取具有较大压摆率的器件,二是在比较器的后端加一级微分电路来提升脉冲信号的边沿。

4)中低频测量精度的影响与消除采用20 MHz数据采样信号来循环计数被测信号的周期及相位差对应的时间差,精度达到0.05 μs,20位数字量的单位是0.05μs。利用被测信号刷新采样计数,实现高频多测量,低频少测量,时间计数精确可靠,这样,FPGA可以为MCU提供稳定的数据。

3 系统硬件电路的设计

3.1 前端信号调理电路的设计

施密特触发器(迟滞比较器)虽然可以很好地消除比较器过零引起的抖动,但是其输出信号和输入信号存在相位差,如果两路被测信号的幅度基本相等且两个施密特触发器的门限电平又很接近,则施密特触发器引入的相位误差对测量系统误差几乎无影响。

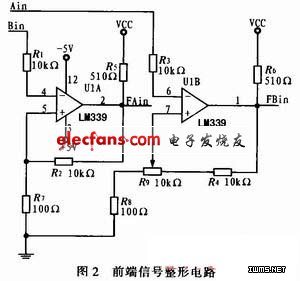

采用LM339内部有4个独立的电压比较器,该电压比较器的特点是:失调电压小,典型值为2 mV;电源电压范围宽,双电源电压为±1~±18 V;对比较信号源的内阻限制较宽。同相和反相输入端电压差别大于10 mV就能确保输出能从一种状态可靠地转换到另一种状态,输出端相当于一只不接集电极电阻的晶体三极管,在使用时输出端到正电源一般须接一只电阻。在跳变电压值附近的干扰不超过回差AU,输出电压的值就将是稳定的。正反馈可以加快比较器的响应速度。由于迟滞比较器加的正反馈很强,远比电路中的寄生耦合强得多,所以可免除由于电路寄生耦合而产生的自激振荡。通过调节电位器,使两个施密特触发器的门限电平基本相等,保证输入电路对相位差测量不带来误差。电路如图2所示。