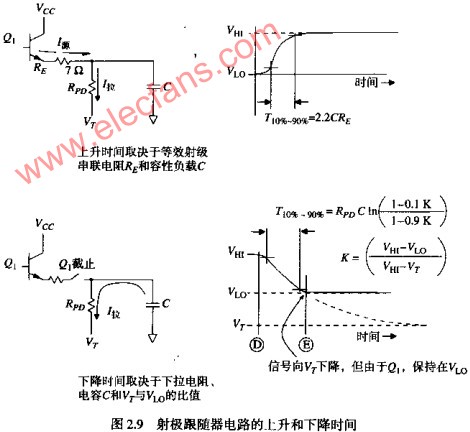

图2.9举例说明了一个ECL或GAAS射极跟随器输出电路。该电路在HI和LO两个状态都有电流流过。

对于10KH和10G产品系列,两者的逻辑HI和LO输出电压都是相近的,尽管不同的ECL和GAAS射极耦合逻辑系列在温度轨迹特性上存在细微的判别。这些逻辑电路通常采用-5.2的电源供电。高电平输出(多数情况下是正的)标称值为-0.9V,而低电平输出为-1.7V。

射极耦合逻辑电路需要有一个下拉电阻,通常用来端接到-5.2V或者中间电压-2.0V。这里我们介绍一下这两种情况下的计算。

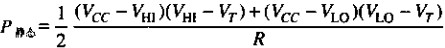

当输出电压通过一个戴维南等效电阻R下拉至VT时:

由-5.2V供电的ECL逻辑电路通过电阻R下拉至-5.2V时,代入这些数值,上式可简化为:

VCC=0(正电压)

VHI=-0.9(标称逻辑高电平)

VLO=-1.7(标称逻辑低电平)

VT=-5.2(下拉电压)

P静态=4.91/R

同样的电路通过电阻R下拉至-2.0V时,式

可以简化为:

VCC=0(正电压)

VHI=0.9(标准逻辑高电平)

VLO=-1.7(标称逻辑低电平)

VT=-2.0(下拉电压)

P静态=0.75/R

对于相同的电阻值,使用-2.0V端接时表现出明显的功耗优势。这是因为当电源电压被下拉到-2.0V时,下拉电阻汲取电流也较小。小电流意味着低功耗。较小的电流还意味着电路从HI转换到LO时需要更长的下降时间。

由于输出电路是一个射随器,上升时间不受下拉电流的影响。图2.9中标明了10KH系列的ECL逻辑晶体管Q1的发射极等效串联电阻RE的阻值约等于7欧,当给负载电容C充电时,源电流远大于下拉电流,因此充电时间常数等于它们的乘积:TRC=REC

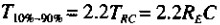

TRC是输出电路从低电平状态上升到高电平的63%时所需的时间。上升到高电平的90%所需的时间将是它的两倍多一点,简单RC电路的10~90%上升时间是:

该时间常数,见上式,通常小于晶体管Q1的开启时间,因此输出电路的上升时间通常等于晶体管Q1的开启时间。

在下降沿,晶体管Q1截止,不再有电流流过发射极。只有电容C通过下拉电阻放电,这就是功率和上升时间的关系开始起作用的地方。下降时间直接与电容C放电的速度成正比。功耗与静态下拉电流成正比。不管下拉电阻是连接到-5.2V,都需要一个大电流迅速地将电容C放电。

图2.9显示了电流衰减的波形。在D时刻,晶体管Q1截止。输出电压在时间常数RPDC内衰减至电压VT。在E时刻,电压已降到VLO,而晶体管Q1开始翻转,阻止了输出电压的进一步衰减,电压始终保持在VLO。

如果Q1完全截止,从10%到90%的下降时间是: