与传统模拟监控系统相比,数字视频监控系统具有诸多优点:

1)把监控录像保存在大容量硬盘上,数字信号存储信息永不丢失,图像质量不下降。

2)数字视频容易被计算机处理。可以在监控图像中设定报警区域,计算机对报警区域的图像进行分析和处理,做到自动监控,无人值守。

3)数字视频经过压缩之后,占用带宽较小,而且数字信号在传输时容易进行加密,非法截取的信号无法还原为视频图像。

4)数字录像存储在计算机硬盘上,可以用计算机来检索和管理,摆脱了手工管理和检索的复杂繁琐。

基于网络摄像机的远程视频监控系统的研究,国外起步较早,成熟的网络摄像机产品有索尼营销公司推出的10BASE2T的网络摄像机“SNC2VL10N”,以及松下KX2HCM130、三星SNC2100P、安特ANT2NWC10/50/100等。国外同类产品一般采用MPEG或者小波压缩方法,性能较好,但价格昂贵,国内用户大都无法承受。我国这方面的研究刚刚起步,大多数厂商仅代理国外产品,从事实际研究的单位不多。

目前国内市场上已经投入使用的视频采集设备多以视频采集卡的形式存在。本文设计的方案采用TI公司的TVP5040作为前端视频采集设备的主体芯片,可以作为独立的单元存在,并且具有体积小、处理能力强且功耗低的特点;加之采用了功能强大的TI嵌入式处理器芯片TMS320DSC21,使系统可以快速、稳定地实现图像数据的采集、压缩和打包上传,为数字化视频监控提供了解决方案。本文中简单介绍了TMS320DSC21,详细介绍了自行研制的远程视频监控系统视频数据采集与处理端的硬件结构,以及运用该系统实现网络实时监控的设计方案。

1 TMS320DSC21微处理器

TMS320DSC21微处理器(简称DSC21)是一个高性能的单芯片微处理器,由以下几部分组成:

1)1个DSP(TMS320C5409)子系统;

2)1个微控制器(ARM7TDMI)子系统;

3)2个DSP协处理器(iMX和VLC);

4)SDRAM控制器;

5)图像外围单元①。

DSC21的高集成度使之特别适合应用于视频、音频和图像类产品。其5个子系统在单个芯片上组成了一个完整的系统。片上MCU运行用户操作系统处理复杂的协议,实现控制功能和位操作;DSP和DSP协处理器完成大运算量计算、数字信号处理以及算术计算;图像外围组件和SDRAM控制器提供极大的数据流量。因此,DSC21可以在单芯片上实现高性能、多处理器的图像处理系统。

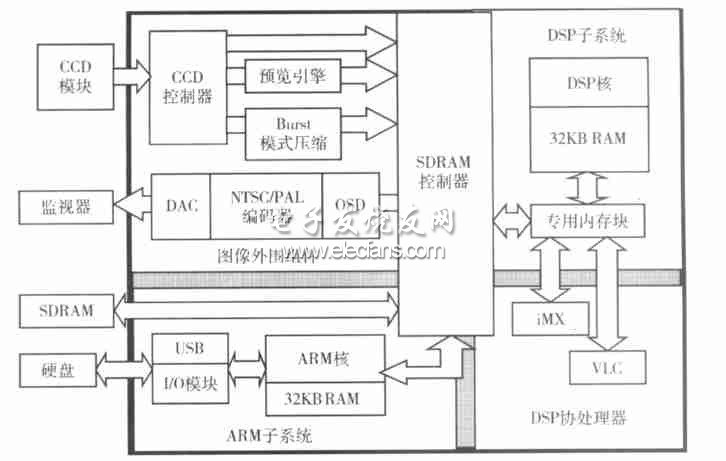

图1示出DSC21模块图

DSC21模块包括:

1)ARM子系统。由ARM7TDMIRISC内核、内部RAM和外设模块组成。ARM子系统完成所有的控制功能,支持实时操作系统,如ucOS,Vx2Works,uITRON,Nucleus和Linux。ARM也控制各个外设模块,如定时器、中断控制器、CCD/CMOS控制器、OSD、NTSC/PAL视频编码器、USB、CF卡、SM卡、IrDA、预览引擎、串口等。用户接口软件也在ARM上运行。

2)DSP子系统。由DSP核、32KBRAM和专用内存块(ImageBuffer)组成。DSP核是一个基于0118μm技术的DSP处理器TMS320C5409DSP。

DSP子系统负责所有大运算量信号处理任务,如图像处理,JPEG压缩;处理所有的实时I/O,如音频和ModEMI/O,MP3,AAC播放的实现;支持可编程实时自动曝光、自动聚焦、自动白平衡(AE,AF,AWB),以及图像/视频拍摄和回放。

3)DSP协处理器。由iMX和VLC两部分组成,负责协助DSP子系统进行图像处理。iMX由4个并行的乘加单元(MAC)组成,适合矩阵运算;而VLC针对JPEG,MPEG1的量化和HufFMan编码进行优化。DSP子系统可以通过调用子程序实现对DSP协处理器的操作。

4)SDRAM控制器。是片外扩展SDRAM与片内所有功能模块的接口。它为片外SDRAM提供与DSC21处理器和图像单元连接的高带宽接口,支持最高80MHz,32bitSDRAM。SDRAM控制器支持实时CCD数据流输入和TV显示数据输出,其访问性能达到320MB·s-1。

5)图像外围组件。DSC21有4个图像单元:

CCD控制器、预览引擎、连拍模式压缩/解压缩单元和硬件图形单元。这些专用的图像单元由ARM控制,用于向DSC21系统读入数据并建立彩色显示。

CCD控制器可以为CCD/CMOS图像传感器提供必要的同步时序逻辑,并支持逐行扫描和隔行扫描CCD/CMOS图像传感器。通过对CCD控制器内部的寄存器进行配置,可以使CCD控制器处于不同的工作状态。CCD控制器能支持高达16Mpix(4K×4K)的CCD/CMOS图像传感器。

预览引擎模块将CCD控制器传来的数据转换成适合NTSC/PAL编码器的显示格式,它可达到实时30帧·s-1的NTSC/PAL预览。预览引擎内置增益控制、白平衡、垂直水平噪声过滤、CFA插值、降采样、伽马校正和色空间转换等功能。

连拍模式压缩解压缩模块采用无损(或有损)算法,将从CCD控制器传来的原始图像数据压缩并写入SDRAM,解压缩引擎在DSP的控制下可以对这些数据解压。这些数据被处理、显示,存回SDRAM。连拍模式可以支持10帧·s-1高分辨率照片的拍摄。

硬件图形单元由3部分组成:OSD(OnScreenDisplay)、NTSC/PAL编码器和DAC(数模转换器)。

OSD支持3个硬件窗口,NTSC/PAL编码器集成了复合视频信号输出通道和独立R,G,B输出通道①。