2 FIash控制器和FPGA器件配置模块设计

2.1 FIash控制器设计

烧写Flash存储器和利用Flash存储器配置FPGA器件时,都需要对Flash存储器进行操作,因此需要设计一个控制器模块来专门产生Flash存储器的控制指令。Flash控制器要实现的功能是:响应输入的擦除、写、读命令,并根据命令产生相应的时序来实现对Flash的操作。

为了在一片Flash存储器中存放多个配置文件,可以将Flash按照配置文件的大小分为多个区间。这样,对于一个具体的配置文件,输入指令的作用范围应该在配置文件存放的区间内。因此,擦除某个配置文件时要选用块擦除方式,而不是整片擦除方式。

为了及时的将一帧配置码流写入Flash存储器中,要求Flash存储器的编程时间应该小于FPGM指令执行后的等待时间。根据Flash存储器数据手册上的参考数据计算后发现,使用普通的编程方式来烧写一帧配置码流时间大于等待时间,而使用写缓冲的编程方式来烧写一帧配置码流的时间要小于等待时间,因此必须选用写缓冲的编程方式来烧写Flash存储器。

JTAG接口与Flash控制器间的命令和数据翻译由反向兼容JTAG控制器中的烧写控制模块完成。它会接收JTAG接口发送的擦除或写命令,经过转化后产生相应的Flash控制器必需的命令、地址和数据。由于一次写缓冲编程写入Flash存储器的数据小于一帧配置码流的大小,因此接收到写命令后,烧写控制模块会配合写命令和对应的操作地址,将缓冲区中一帧配置码流分多次送往Flash控制器。

2.2 FPGA器件配置模块设计

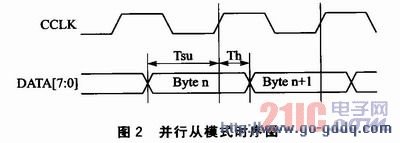

Virtex系列FPGA器件的配置模式共有4种:串行主模式、串行从模式、并行从模式和边界扫描模式,其中主模式使用内部振荡器提供时钟,从模式和边界扫描模式使用器件外部提供的时钟。在FPGA器件上电初始化后,配置模块向FPGA发送配置码流和配置时钟来配置FPGA器件。因为配置速度越快FPGA器件工作前的等待时间就越短,所以本方案选择速度最快的并行从模式。图2是并行从模式的时序图,数据(DATA[7:O])必须满足建立时间(Tsu)和保持时间(Th)的约束。FPGA器件配置模块配置FPGA器件的步骤如下:

①FPGA器件配置模块检测到INIT引脚信号变高,说明FPGA器件的上电后自动初始化已完成,配置模块向Flash控制器发送读命令;

②配置模块收到Flash控制器返回的配置码流后,在每个时钟上升沿向FPGA器件发送一个8位配置码流;

③配置模块检测到DONE引脚信号变高,说明FPGA器件已配置完成,配置过程结束。

由于从向Flash控制器发送读命令到Flash控制器返回配置码流的时间大于一个周期,且返回数据的位宽大于并行从模式的数据位宽,因此必须先对配置码流进行位宽转换。同时,为了保证CCLK的每个始终上升沿都有一个8位配置码流发送出去,还必须对CCLK进行合适的分频。