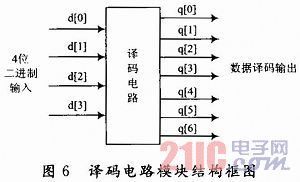

2.2.4 译码电路模块

译码电路模块可对表示十进制数的4位二进制代码进行编码,此模块可直接连接数码管驱动器,从而驱动数码管显示出相应的阿拉伯数字等字符。与锁存器电路模块设计一样,它也只需要先设计一个单个的译码器,然后通过连接组合就可构成译码电路模块,从而实现译码功能。为实现其功能,单个译码器需要设置4个数据输入端:即d[0],d[1],d[2]和d[3],并由这些端口输入锁存电路模块输出的4位二进制数据,需要设置7个输出端:即q[0],q[1],q[2],q[3],q[4],q[5]和q[6],它们分别连接7段数码管的7个显示输入端。译码电路模块中单个译码器符号及端口功能如图6所示。

3 软件设计

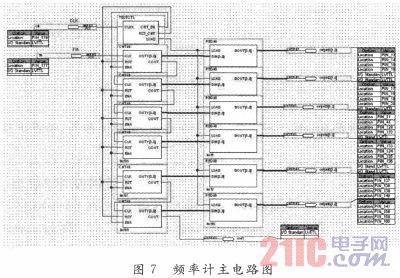

根据前面的分析,采用VHDL语言设计一个简易的数字频率计,运用自顶向下的设计思想,将系统按功能逐层分割的层次化设计方法进行设计。在顶层对内部各功能块的连接关系和对外的接口关系进行了描述,而功能块的逻辑功能和具体实现形式则由下一层模块来描述。即控制、计数、锁存、译码四个实现数字频率计的核心模块,然后根据图2可以将上述四个模块VHDL源程序作为底层元件,使用QUARTusⅡ开发工具,用该工具软件所支持的语言——硬件描述语言VHDL,以文本的方式进行编程输入。在编程时分别对控制、计数、锁存、译码等电路模块进行VHDL文本描述,使每个电路模块以及器件都以文本的形式出现,然后通过编译、波形分析、仿真、调试来完善每个器件的功能。单个器件制作完成后,然后将它们生成库文件,并产生相应的符号,最后用语言将各个己生成库文件的器件的各个端口连接在一起,从而形成了频率计主电路的软件结构。在连接器件时,采用图形输入方式,即在图形输入界面中调出先制作好的库文件器件符号,再将每个器件符号的各端口直接连线,从而构成频率计主电路图。频率计主电路图如图7所示。仿真波形如图8所示。