・上一文章:系统设计师的数字电源

・下一文章:基于ARM的GPS同步授时系统设计

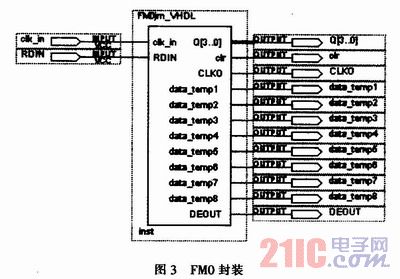

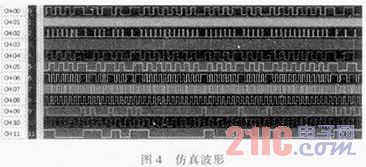

以BST信号为例,解码数据输入端RDIN输入BST信号,在解码时钟输入端clk_in输入16倍数据速率时钟信号(4 096 kB/s)。在QuartusⅡ软件支持下完成逻辑综合,将编程数据写入选定的FPGA芯片进行测试,可通过逻辑分析仪看到波形。

图4依次给出了RDIN、clk_in、clr、data_temp1、data_temp4、data_temp5、data_temp6、Q1、Q2、Q3、CLKO和DEOUT的仿真波形。从仿真结果来看,解码模块很好地完成了任务,可测得整个解码过程仅用了8 μs。

同样的解码过程用现有的图形输入法完成需要40μs,而用VHDL语言编写只需8 μs,解码时间是图形输入法的五分之一。

5 结束语

采用高级硬件描述语言VHDL在FPGA上实现FM0解码设计,为电子系统的设计带来了极大地灵活性。将复杂的硬件设计过程转化为在特定的软件平台上通过软件设计来完成,从而使设计工作简化,大大节约了开发时间,并大幅度缩短FM0解码时间。

随着ETC系统的日益普及,对FM0解码设计的需求也大幅提高,因此采用较合适的方法设计出高性能的FM0解码器是十分有意义的。