目前,变频调速一般采用微处理器和专用芯片来实现。但是普通的专用芯片运算速度受微处理器系统时钟影响,且开发周期长,硬件调试不方便[1]。随着微电子技术和EDA软件的发展,出现的FPGA几乎克服了所有这些不足,所以本设计采用了FPGA方案。

三相SPWM的产生一般可以通过三相相位上互差120°的正弦波与三角波比较来实现。三相正弦表可以由三个独立的相位互差120°的正弦表组成,这在设计思路上是简单的,但实际中却有很大的浪费。

目前有人采用了分时复用的方法来减少三相正弦表所占用的逻辑门[1]。从正弦波的波形可以看出,正弦波具有很好的对称性,还能对正弦表再进行优化。

因此,本文提出了利用分时复用以及正弦波的对称性,对三相正弦表进一步优化,以进一步减少正弦表所占用的逻辑门,提高FPGA的利用率。

1 数据的合成

数据合成由分时复用电路和运算电路两部分组成。通过分时复用,使得所需的正弦表减少到原来的1/3,即产生三相正弦波只需一个正弦表。运算电路利用正弦波的对称性,使得实现一个完整周期的正弦波只需1/4周期的正弦表。两者结合,从而完成三相正弦波只需一个1/4周期的 正弦表,达到最大程度的节省资源的目的。

1.1 分时复用原理及其应用

分时复用的原理是各路信号占用同一信道的不同时间间隙进行信号传输。具体到本电路就是利用对正弦表寻址的高速度,使一个正弦表在不同时间段查询不同相的正弦波的幅值,以达到减少正弦表所占用的FPGA资源的目的。

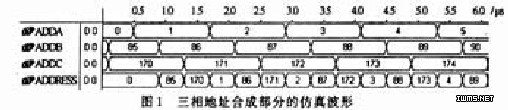

电路的具体实现:三路在相位上互差120°的地址数据并行输入,通过一个三选一的选择器来进行选择,选择器的控制端接三进制的计数器[1]。如,计数器为0时,输出的是A相的地址。计数器为1时,输出的是B相的地址。计数器为2时,输出的是C相的地址。因此只要使输入的三相地址周期性变化,就实现了并行输入的三相地址数据在时间上形成了连续,也就实现了三相地址数据的合成。这样就可以利用一个正弦表来得到三相的正弦值。把正弦表减少到没有采用分时复用时的1/3。该部分电路的仿真波形如图1所示。图中ADDA,ADDB,ADDC分别为A相,B相和C相的相位值。ADDRESS为合成一路后的相位值。

1.2 正弦波的对称性及其应用

由正弦波波形可知,正弦波具有很好的对称性。π/2~π的幅值大小与0~π/2的幅值大小相同,只是他们在时间上出现的顺序刚好相反。π~3π/2的幅值与0~π/2的幅值的绝对值相同,极性相反。3π/2~2π部分的幅值与π~3π/2的大小相等,只是时间上出现的顺序相反。因此,根据正弦波的对称性,只在正弦表ROM中存有相位0~π/2时的幅值。利用0~π/2相位时的幅值产生完整的正弦波波形。 产生正弦波首先需要对正弦表进行寻址,把量化的相位值转化为对应的量化的幅值。由于正弦表ROM中仅存有相位0~π/2时的幅值,而π/2~π,3π/2~2π的绝对值与相位0~π/2的幅值在时间上出现的顺序相反,因此,要获得π/2~π,3π/2~2π的幅值必须对相位0~π/2时的幅值进行反向寻址。反相寻址通过地址输入矢量取反来实现[2]。本设计把周期2π量化为8位,即对一个正弦波周期进行256次取样。因此对0~π/2相位寻址所需的地址线为64条。ADDRESS定义为STD_LOGIC_VECTOR(7DOWNTO0),ADDRESS低6位用于对ROM表进行寻址,当地址数据ADDRESS(6)为“1”时,对地址ADDRESS的低6位取反再对ROM寻址。

正弦波的负半周的形成。由于负半周的幅值与正半周的幅值在极性上相反,因此对输出的对应的幅值取反。幅值是否取反由输入的地址数据ADDRESS(7)决定,当ADDRESS(7)为“1”时,对应的输出幅值取反[2]。并把ADDRESS(7)取反作为最终输出的正弦波幅值的最高位。这样做实际上把正弦波向Y轴正方向平移了一个幅值,避免了幅值出现负值。