・上一文章:第四代移动通信系统关键技术研究

・下一文章:应用多个单片机的液位监控仪

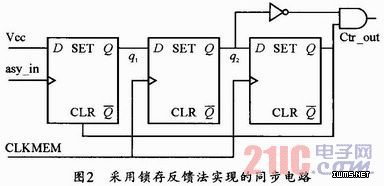

图1、图2所示的电路,在接收方的时钟域采用两级触发器,大大增加了同步器的平均失效时间MTF(mean time to failure),MTF的有关计算公式在文献中给出。计算表明,对于大多数的应用,两级锁存器同步失效的概率很小,足以消除可能出现的亚稳态情况。

2 数据通路的同步

数据在不同时钟域之间的传递,一般不采用上述的同步器,因为多位数据的同时变化会使同步器的采样错误率大大增加。本文采用异步FIFO实现数据通路的同步。

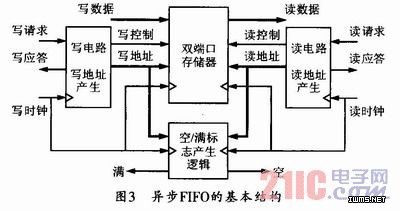

2.1 异步FIFO

异步FIFO是一种先进先出的电路,发送方时钟域先把数据存储到RAM,稳定后再读取到接受方时钟域,从而实现异步数据的可靠传输。一般由读、写电路和FIFO存储体组成,如图3所示。