����AD9852��Ҫ�ɲο�Ƶ��Դ����λ�ۼ��������δ洢��(���Һ������ܱ�)����ģת��������ͨ�˲�����ɡ��ο�Ƶ��ԴΪDDS�ṩ����ʱ��Ƶ�ʣ�DDS����ĺϳ��źŵ�Ƶ���ȶ����ڲ������ڲ����總����λ�����Ȼ��ڵ�Ӱ��ʱ���Ͳο�Ƶ��Դ��һ���ġ�

������Ƶ�ʱ任�����У�100Hz��1kHz���������DZȽϹؼ��ļ���ָ�꣬����DDS���ɵ��ۺ������ԣ���ȡ����DDS����źŵ����롢�˲���·�������Լ��Ŵ��·�ĸ�������ȣ���������Ǹ���ʵ����Ƶ��˲����Ŵ��·�����ģ����ڵ�һ����ȡ����ʵ�ʲ��õ�оƬ���ࡣͼ2Ϊһ��DDS���������ͼ��

����

����ͼ2 DDS����Ա�ͼ

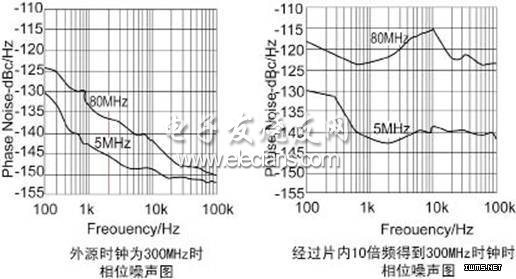

������ͼ2�ɼ��������ڲ���Ƶ�ķ�ʽ��ƫ��1kHz�����5MHzʱ����Ϊ��140dBc/Hz;��ֱ�Ӳ���300MHz��ʱ��ʱ�������������ƫ��1kHzʱΪ��142dBc/Hz����ˣ�Ϊ�����DDS����źŵ��������ܣ������ⲿ��Ƶ����һ���ȽϺõ�ѡ��������ʱ���ź����ⲿ����N��Ƶ��ӵ�DDS�ϡ�

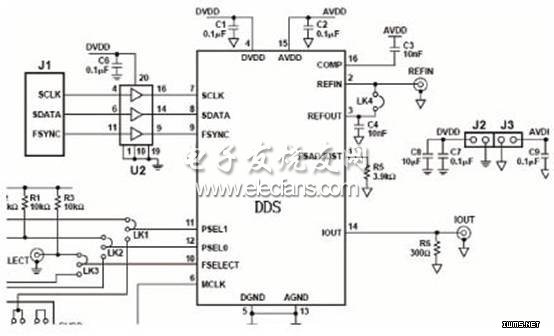

����DDS��ʹ��ʱ��Ҫͨ����������CPLD�����źš����ݽ��й���������ʵ�־���Ӧ��������Ҫ�����ɹ��ܣ�ͼ3Ϊ����ѡ�õ�һ��DDSоƬ��Χ��·ʾ��ͼ��

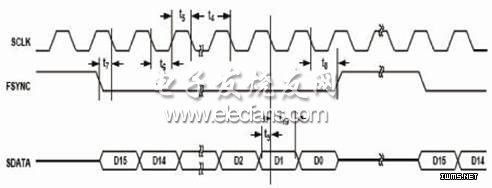

�������У�MCLK���Ž��ⲿʱ��Դ��ʹDDS��IOUT���������Ƶ���źŵ��ȶ������ⲿʱ��Դһ�¡������ڲ�û��PLL��Ƶ���ڵ�DDSоƬ��ͨ��MCLK������ʱ��Դ��Ƶ��Ӧ����IOUT������ź�Ƶ�ʵ�4����������ź�Ƶ��Ϊ5.3125MHz����ôMCLKʱ�Ӷ˵��ź�Ƶ��Ӧ�ô���20MHz���������õ����õ���λ������ͨ���ⲿ�˲���·�ɵõ��Ƚϴ������ź��ס�FSELECTΪ���ص�Ƶ�ź�����ˣ�Ҳ�������ǵĵ��Ʒ���79Hz�ź�����ˣ�����ʹ�õ�DDS�ڲ�������Ƶ�ʿ��ƼĴ�����ͨ����̵ķ�ʽ��Ԥ�����úõ�Ƶ��ֵF0��F1�����ڼĴ����У���FSELECT�����з����ź�����ʱ(����ƽ�����ػ��½���ת��)��DDS��IOUT�˽�����֮�ֱ��Ƶ�ʿ��ƼĴ����ж���F1��F0��ֵ��Ϊ��������һᱣ��Ƶ���ź����л�ʱ��λ�ޱ仯��PSEL1��PSEL0Ϊ��·�ź�Ƶ��F1��F0����λ���ڶˣ���Ӧ���У������Ҫ����F1��F0���л�ʱ����λ��������Ҫ�������ֱ�ӽ�PSEL1��PSEL0�ӵء�DDS�����ͨѶ��ʱ����ͨ������FSYNC��SCLK��SDATA����ɵģ��䴮��ͨѶ��ʱ����ͼ4��ʾ��

������FSYNCΪ�ߵ�ƽʱ��SCLK��SDATA����Ϊ����״̬����FSYNCΪ�͵�ƽʱ��DDS������ͨѶ״̬����ʱ����SCLK��һ�½��ص�����ʱ����ʹ������������SDATA�ϵ�DATAд��DDS���ݻ�������ֱ������һ��DATAд��ʱ��DDS����������FSELECT�ϵ�״̬ѡ��F1��F0��ΪIOUT�˵������

�����źŵIJ���

��������ѡ�õ�DDSоƬ�ڲ���2��32λƵ�ʿ��ƼĴ���(F0��F1)������ͼ4�Ĵ���ͨѶʱ����SDATA��ʵ����Ҫͨ�ŵ�DATAλ����32λ������MCLK�ⲿ����ʱ��Ƶ��Ϊ20MHz��DDS����С��Ƶ�ʷֱ���Ϊ��

����

����IOUT���20MHzʱ(ʵ�����Dz����ܵģ�����������ź����dz���)����Ӧ��32λƵ�ʿ��ƼĴ�����ֵȫΪ1;���5.3125MHzʱ����Ӧ��ֵΪ(5.3125MHz/20MHz)×232�������õ���ʮ����ֵת��Ϊ�����ƶ�Ӧ32λƵ�ʿ��ƼĴ�����ֵ������ͼ4�Ĵ���ʱ��ͨ������������Ӧ��32λֵд��DDS����������IOUT���Ŷ˽������5.3125MHz���Ҳ�Ƶ���źŵ����������ֵ��50ŷķ���ص������Ϊ1V���ң�����ķ�ȡ����ĵ�ƽ����ͨ������FSADJUST�˵���ӵ���ֵ���е��ڡ�

�����ھ����ʵ��Ӧ���У��������5.3125MHz���Ҳ��źţ���Ҫ�����˲������Ρ��Ŵ�ȴ�����������뵽������·�����С������ʱ��Ϊ�õ��Ƚϴ������ź��ף���IOUT�������ͨ�����ǽ�һ��ͨ�˲������ͨ�˲�����

����

����ͼ3 DDS��Χ��·ԭ��ͼ

����

����ͼ4 DDS����ͨѶʱ��ʾ��ͼ