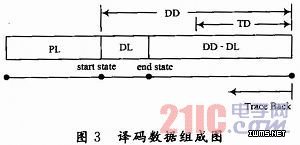

将其处理成图中所示的待译码数据格式,其中DL是实际输入的所需译码数据长度,PL为所需在数据中加的数据前缀长度,也即上述固定延迟算法中的头译码长度,DD为所要达到的译码深度(Decoding Depth),DD-DL为所要加的后缀长度,即固定延迟算法中的尾译码长度。在设计中选择PL为96,由于在LTE系统中DL是变化的,最大为76,不能够选择固定的尾译码长度,但在本文设计中选择固定的DD为192。

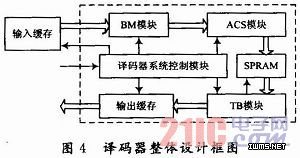

译码器的整体设计框图,如图4所示。图中译码器主要由译码器系统控制模块,分支度量(BM)模块,加比选(ACS)模块,回溯(TB)模块和输出缓存组成。

数据处理由译码器系统控制模块控制完成,它控制从输入缓存中读入数据进行译码。

下面对译码器BM模块、ACS模块和TB模块这三个核心模块的具体设计与实现进行详细介绍。

3.1 BM模块

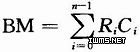

在整个系统中分支度量采用的是软判决数据。软判决根据接收的的软判决比特和编码器网格图的参考分支,计算其欧氏距离。一般的欧氏距离采用如下公式计算:

![]()

式中:ri为接收的软判决比特;ci为编码器网格图的参考分支。上述公式经简化后结合系统所用软判决数据特点,可以得到如下计算方法:

式中:Ri为接收的软判决比特的绝对值;Ci∈{0,1)为参考分支比特。

3.2 BM模块

在每一个时钟中,用得到的分支度量(BM)和路径度量(PM)相加,得到下一时刻状态的多个路径度量,通过比较,选择一个幸存分支。将每个状态的幸存分支,存储到回溯存储器中,更新路径度量。在设计中,存储从数据段(即图4中的Initial State)开始,在这之前的幸存分支不需存储。同时,计算出64个状态中,具有最小路径度量的状态。

如果直接将前一状态的路径度量与分支度量相加,得到下一状态的路径度量,来选择幸存分支,如图2中,比较PMi+BMp和PMj+BMq选择幸存分支。每个状态2个加法器,64个状态就需要128个加法器。