CPLD设计的 数码管 驱动显示 电路

1.1 显示原理:

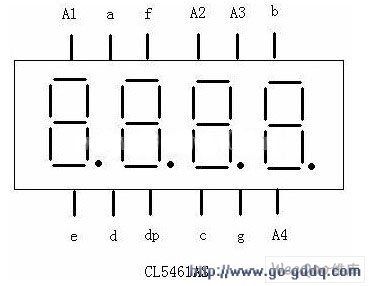

八段数码显示管如图1.1 所示, 八段数码管 每一段为一发光 二极管 ,共有a~g 以及小数点dp 八个 发光二极管 。将八段数码管中的每个二极管的阴极并联在一起,组成公共阴极端。这样把共阴极管脚接地,此时哪个管脚输入高电平,对应发光二极管就被点亮。

图 1.1 八段数码显示管

CL5461AS 数码管管脚图如图1.2 所示,它将四个数码显示管的a~g 及小数点dp 管脚并联在一起,作为数码管数据输入端;分别引出各个数码管的阴极A1~A4。

图1.2 CL5461AS 数码管管脚图

只要在A1~A4 管脚上轮流加低电平其频率大于40Hz,可实现四个数码管同时被点亮的视觉效果。在点亮不同数码管的同时输入不同的数据,即可在数码管上同时显示四位不同的数字。例如:四个数码管要显示9876 数字。第一个数码管A1 加低电平,其余A2、A3、 A4高电平,同时数码管输入和9 对应的数据;然后第二个数码管A2 加低电平,其余A1、A3 、A4 高电平,同时数码管输入和8 对应的数据;然后第三个数码管A3 加低电平,其余A1、A2 、A4 高电平,同时数码管输入和7 对应的数据;然后第四个数码管A4 加低电平,其余A1、A2 、A3 高电平,同时数码管输入和6 对应的数据;周而复始重复上述过程,四个数码管就显示9876 数字。

1.2 驱动八位数码管显示电路框图

用CPLD 设计一个驱动八位数码管显示电路。八位数码管管脚图如图1.2 所示。

用两个CL5461AS 数码管接成一个八位数码管显示,将两个CL5461AS 数码管的a~g 及小数点dp 管脚并联在一起,两个CL5461AS 数码管的阴极A1~A4 定义为Vss0、Vss1、Vss2、Vss3、Vss4、Vss5、Vss6、Vss7。

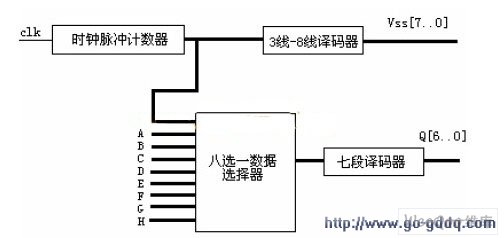

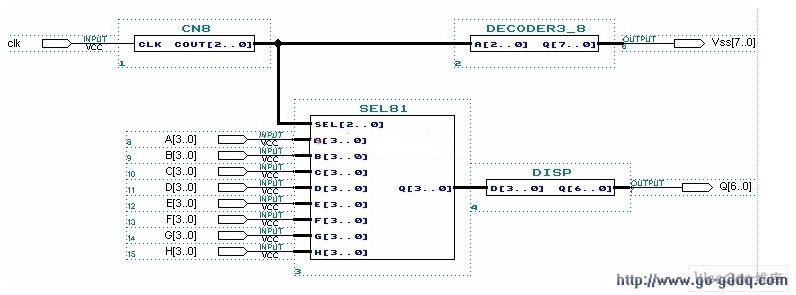

用CPLD 设计一个驱动八位数码管显示电路的框图如图1.4 所示。

图1.4 驱动八位数码管显示电路框图

时钟脉冲 计数器 的输出同时作为 3 线―8 线译码器、八选一数据选择器地址码的输入。

时钟脉冲计数器的输出经过3 线―8 线译码器译码其输出信号接到八位数码管的阴极Vss0、Vss1、Vss2、Vss3、Vss4、Vss5、Vss6、Vss7 端。要显示的数据信息A~H中哪一个,通过八选一数据选择器的地址码来选择,选择出的数据信息经七段译码器译码接数码管的a~g 管脚。这样八个数码管就可以轮流显示八个数字,如果时钟脉冲频率合适,可实现八个数码管同时被点亮的视觉效果。

1.3 模块及模块功能:

1.3.1 时钟脉冲计数器模块

时钟脉冲计数器模块CN8 如图1.5 所示。CN8 模块输入信号是时钟脉冲clk,其频率大于40Hz,每遇到一个时钟脉冲clk 上升沿,内部累加器便加一,再把累加器所得结果以2进制数的形式输出。要显示八位数字,所以用3 位2 进制数作为输出。输出信号为cout[0..2]。

图 1.5 时钟脉冲计数器模块CN8

library ieee;

use ieee. ST d_logIC_1164.all;

use ieee.std_logic_unsigned.all;

entity cn8 is

port (clk:in std_logic;

cout:out std_logic_vector(2 downto 0));

end cn8;

architecture rtl of cn8 is

signal q: std_logic_vector(2 downto 0);

begin

process (clk)

begin

if (clk'event and clk='1' ) then

if (q=7) then

q<="000";

else

q<=q+1;

end if;

end if;

end proc ESS ;

cout<=q;

end rtl;

1.3.2 3-8 线译码器模块

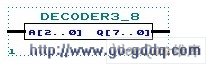

3-8 线译码器模块DECODER3_8 如图1.6 所示。DECODER3_8 模块的输入端是A[2..0]接收时钟脉冲计数器CN8 模块的输出信号,经过译码后输出信号Q[7..0]分别接八个数码管的阴极Vss7、Vss6、Vss5、Vss4、Vss3、Vss2、Vss1、Vss0,使对应的数码管的阴极为低电平,对应的数码管被点亮。要显示八位数字,需要八个输出端,所以做成3-8 线译码器。

图 1.6 3-8 线译码器模块DECODER3_8

library ieee;

use ieee.std_logic_1164.all;

entity decoder3_8 is

port(a:in std_logic_vector(2 downto 0);

q:out std_logic_vector(7 downto 0));

end decoder3_8;

architecture rtl of decoder3_8 is

begin

process(a)

begin

case a is

when "000"=>q<="11111110";

when "001"=>q<="11111101";

when "010"=>q<="11111011";

when "011"=>q<="11110111";

when "100"=>q<="11101111";

when "101"=>q<="11011111";

when "110"=>q<="10111111";

when thers=>q<="01111111";

end case;

end process;

end rtl;

1.3.3 八选一数据选择模块

八选一数据选择模块 SEL81 如图1.7 所示。SEL81 模块输入信号一个是数据选择器SEL81的地址码SEL[2..0],另一部分是数据信息A[3..0] ~H[3..0]。地址码SEL[2..0]来自时钟脉冲计数器CN8,由地址码SEL[2..0]决定输出哪个输入数据。输出信号是Q[3..0]。

图 1.7 八选一数据选择模块SEL81

library ieee;

use ieee.std_logic_1164.all;

entity sel81 is

port(sel:in std_logic_vector(2 downto 0);

a,b,c,d,e,f,g,h:in std_logic_vector(3 downto 0);

q:out std_logic_vector(3 downto 0));

end sel81;

architecture rtl of sel81 is

begin

process(a,b,c,d,e,f,g,h,sel)

variable cout: std_logic_vector(3 downto 0);

begin

case (sel) is

when "000"=>cout:=a;

when "001"=>cout:=b;

when "010"=>cout:=c;

when "011"=>cout:=d;

when "100"=>cout:=e;

when "101"=>cout:=f;

when "110"=>cout:=g;

when thers=>cout:=h;

end case;

q<=cout;

end process;

end rtl;

1.3.4 七段译码器模块

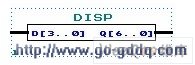

七段译码器模块 DISP 如图1.8 所示。DISP 模块是七段译码器,将输入的4 位二进制数转换为数码显示管所对应的数字。例如输入为4 位二进制数0000 的时候,使数码显示管显示0,则要七段译码器输出为0111111,即g 段为0,g 段发光二极管不亮,其他发光二极管被点亮,显示效果为0。DISP 模块输入信号D[3..0]接到八选一数据选择模块的输出信号Q[3..0];七段译码器输出信号Q[6..0]接数码管的a~g 管脚。

图 1.8 七段译码器模块DISP

library ieee;

use ieee.std_logic_1164.all;

entity disp is

port(d:in std_logic_vector(3 downto 0);

q:out std_logic_vector(6 downto 0));

end disp;

architecture rtl of disp is

begin

process(d)

begin

case d is

when"0000"=>q<="0111111";

when"0001"=>q<="00 0011 0";

when" 0010 "=>q<="1011011";

when"0011"=>q<="1001111";

when" 0100 "=>q<="1100110";

when"0101"=>q<="1101101";

when"0110"=>q<="1111101";

when"0111"=>q<="0100111";

when" 1000 "=>q<="1111111";

when thers=>q<="1101111";

end case;

end process;

end rtl;

1.3.5 驱动八位数码管显示的整体电路

将各个模块连接起来构成整体电路图如图 1.9 所示,可以实现用CPLD 设计一个驱动八位数码管显示电路的功能。clk 是时钟脉冲输入信号,经过时钟脉冲计数器CN8 模块,将信号以3 位2 进制数的形式输出,输出信号是COUT[2..0]。时钟脉冲计数器CN8 的输出同时作为3 线―8 线译码器DECODER3_8 和八选一数据选择器SEL81 地址码SEL[2..0]的输入。时钟脉冲计数器CN8 的输出经过3 线―8 线译码器DECODER3_8 译码其输出信号Vss[7..0]接到八位数码管的阴极Vss7、Vss6、Vss5、Vss4、Vss3、Vss2、Vss1、Vss0 端,决定点亮哪位数码管。同时时钟脉冲计数器CN8 模块输出的信号也进入数据选择器SEL81 地址码SEL[2..0]的输入,进行输出数据的选择,其输出是Q[3..0]。八选一数据选择器SEL81 模块的输出是Q[3..0]再经过七段译码器DISP 模块,将其翻译成可以用数码显示管的数据。七段译码器DISP 模块的输出Q[6..0]分别经300 欧 电阻 接数码显示管的a~g 管脚。八选一数据选择器模块的输入端,可根据具体需要进行设计。

图 1.9 驱动八位数码管显示的整体电路