TCLKA_DELAY=TCO_CLKA+Tflt_CLKA

接收时钟CLKA下一个周期的总延时为:

TCLKA_DELAY=TCYCLE+TCO_CLKA+Tflt_CLKA

要满足数据的建立时间则必须有:

TCLKA_DELAY_MIN-TDATA_DELAY_MAX-Tsetup-Tmargin>0

展开并考虑时钟的抖动Tjitter等因素整理后得到:

式(1)中TCYCLE为时钟的一个时钟周期;第一个括号内是时钟芯片CLOCK BUFFER输出时钟CLKA、CLKB之间的最大相位差,即手册上称的output-output skew;第二个括号内则是CLOCK BUFFER芯片输出的两个时钟CLKA、CLKB分别到达RECEIVER和DRIVER的最大延时差。式(1)中TCO_DATA是指在一定的测试负载和测试条件下,从时钟触发开始到数据出现在输出端口并到达测试电压Vmeas(或VREF)阈值的时间间隔,TCO_DATA的大小与芯片内部逻辑延时、缓冲器OUTPUT BUFFER特性、输出负载情况都有直接关系,TCO可在芯片数据手册中查得。

由公式(1)可知,可调部分实际只有两项:Tflt_CLKB_MIN-Tflt_CLKB_MAX和Tflt_DATA_SETTLE_DELAY_MAX。单从满足建立时间而言,Tflt_CLKA_MIN应尽可能大,而Tflt_CLKB_MAX和Tflt_DATA_SETTLE_DELAY_MAX则要尽可能小。实质上,就是要求接收时钟来得晚一点,数据来得早一点。

1.2 数据保持时间的 时序 分析

为了成功地将数据锁存到器件内部,数据信号必须在接收芯片的输入端保持足够长时间有效以确保信号正确无误地被时钟采样锁存,这段时间称为保持时间。在公共时钟总线中,接收端缓冲器利用第二个时钟边沿锁存数据,同时在驱动端把下一个数据锁存到数据发送端。因此为了满足接收端保持时间,必须保证有效数据在下一个数据信号到达之前锁存到接收端触发器中,这就要求接收时钟CLKA的延时要小于接收数据信号的延时。由图1中的时序关系图中,可以得到时钟 CLKA的延时:

TCLKA_DELAY=TCO_CLKA+Tflt_CLKA

而数据延时:

TDATA_DELAY=TCO_CLKB+Tflt_CLKB+TCO_DATA+Tflt_DATA_SWITCH_DELAY

若要满足数据的保持时间,则必须有:

TDATA_DELAY_MIN-TCLKA_DELAY_MAX-Thold-Tmargin>0

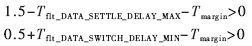

展开、整理并考虑时钟抖动Tjitter等因素,可得如下关系:

式(2)中,第一个括号内仍然是时钟芯片CLOCK BUFFER输出时钟之间的最大相位差;第二个括号内继续可以理解为时钟芯片输出的两个时钟CLKA、CLKB分别到达RECEIVER和DRIVER的最大延时差;要满足数据的保持时间,实际可调整的部分也只有两项,即Tflt_CLKB_MIN-Tflt_CLKA_MAX和Tflt_DATA_SWITCH_DELAY_MIN。单从满足保持时间的角度而言,Tflt_CLKB_MIN和Tflt_DATA_SWITCH_DELAY_MIN应尽可能大,而Tflt_CLKA_MAX则要尽可能小。也就是说,若欲满足保持时间,就要使接收时钟早点来,而数据则要晚点无效(invalid)。

为了正确无误地接收数据,必须综合考虑数据的建立时间和保持时间,即同时满足(1)式和(2)式。分析这两个不等式可以看出,调整的途径只有三个:发送时钟延时、接收时钟延时和数据的延时。调整方案可这样进行:首先假定发送时钟延时严格等于接收时钟延时,即(Tflt_CLKA_MIN-Tflt_CLKB_MAX)=0和(Tflt_CLKB_MIN-Tflt_CLKA_MAX)=0(后文将对这两个等式的假设产生的时序偏差进行考虑),然后通过 仿真 可以得出数据的延时范围,如果数据延时无解则返回上述两个等式,调整发送时钟延时或接收时钟延时。下面是宽带网交换机中GLINK总线公共时钟同步数据收发的例子:首先假定发送时钟延时严格等于接收时钟延时,然后确定数据的延时范围,代入各参数,(1)和(2)式分别变为:

在不等式提示下,结合PCB布局实际,确定Tflt_DATA_SETTLE_DELAY_MAX<1.1;Tflt_DATA_SWITCH_DELAY_MIN>-0.1,剩下0.4ns的余量分配给了两个时钟的时差和Tmargin。在SPECCTRAQUEST中提取拓扑并进行信号完整性仿真,进而 确定各段线长及拓扑结构。对此结构(共12种组合)进行全扫描仿真,得到:Tflt_DATA_SETTLE_DELAY_MAX=1.0825, Tflt_DATA_SWITCH_DELAY_MIN =-0.0835004,符合确定的1.1和-0.1的范围指标。由此可以得出GLINK总线数据线的约束规则:①匹配电阻到发送端的延时不应大于0.1ns;