·上一文章:用万用表指示的齐纳电压检测器

·下一文章:可产生微弱电流的交流恒定电流源

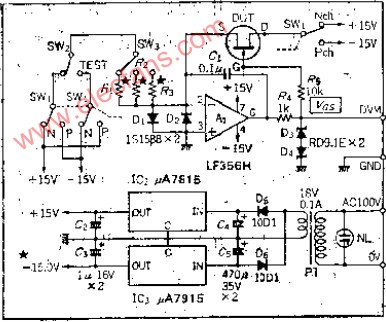

电路的功能

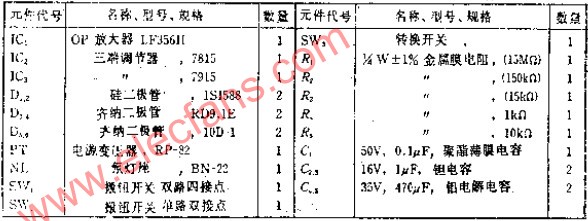

场效晶体管漏极饱和电流IDSS和夹断电压VP等有很大差别,所以确定置偏很麻烦。虽然在生产厂已分了几种等级,但一个等级内仍有差别,如果在组装电路之前测量实际工作电流状态下的VP和VOS则比较方便。测量时,用转换开关选择电阻R1~3,设定工作电流,R值可用R=15/ID计算。

电路工作原理

在OP放大器反相放大电路中,使流过反馈回路的电流与输入电阻确定的电流相等,因此FET漏极电流EB由栅极电压VGS确定。即OP放大器A1构成伺服电路,用A1的输出控制反相输入端的电位,使基等于零。

齐纳二极管D3和D4产生±9V的电压对被测对象(DUT)的栅极电压进行拖箝位使电路不至加异常电压。R5是限流电阻,用来控制栅极电流,使基不至过大(通常几乎无电流流过)。

FET有N沟道和P沟道两种型式,因此可用SW1切换输入电压的极性,满足这两种型号的需要。测试开关SW2在无DUT时,栅极端子电压高于夹断电压,OP放大器的输出对于NOA来说为负,对于POH为正,在进行正常测试时,OP放大器输出为VGS。工作电流ID为1UA时,R1=15/10的-6次方=15M,IB=100UA时,R2=15/10的-4=150K,ID为1MA时,R3=15/10的3次方=15K,应根据使用要求计算R1~R3。

注释

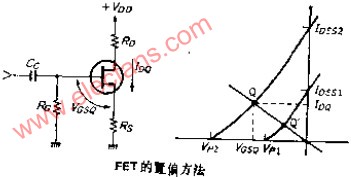

FET的自编电路

图中所示为普通N沟通J-FET自偏电路,由于夹断电压VP或漏极饱和电流IDSS的误差,使置偏点Q发生变化。

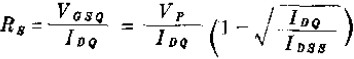

若把源极电阻RS两端产生的电压作为栅极置偏,设定Q点,考虑VP和IDSS的影响后,可用下式大约计算出RS

RS越大,越能吸收误差,但由于受工作电流IDQ的限制,须选用适当的阻值或改用固定置偏电路。