3 利用电容模型分析PCB中的环流问题

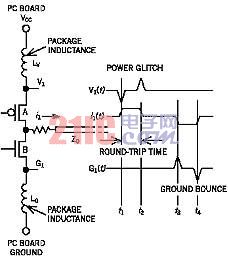

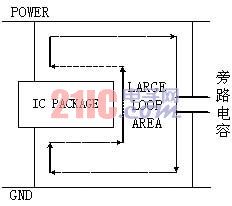

电源去耦电容放置位置不当将会在印制电路板上产生很大的电流环。为了减少噪声,在高速印制电路板的设计当中,有一个很重要的原则是:减少信号电流环的面积。过去我们习惯于只考虑电流的流出起点、途径及终点,而很少去考虑电流的返回路径。在高频电路中,通常认为电源和地是等价的,因此电流的流出途径和返回途径将形成一个电流环,在这些电流环中,会由于种种原因,例如电容的寄生电感,PCB连线的固有电感等,使得环路的阻抗不为零,这样电流流经这一环路时将产生电势差,如果电流是变化的,则将产生辐射,对系统产生干扰。为了给电源滤波,在电路设计中常常要在电源和地之间加上一些旁路电容,在回路中增加旁路电容主要有两个目的,一是增加环路中存储电荷的能力,以免瞬间电流过大,产生地弹噪声。二是适当的放置旁路电容的位置,可为噪声信号提供就近的地回路,减少电流环路的面积,从而减少了环路的电感。采用了旁路电容的回路中,由于欲滤除的噪声频率通常是高频交流信号,因而这样的回路仍旧将会对外产生辐射。为了减少这一辐射,我们需要尽可能的降低回路的阻抗,必须合理放置旁路电容的位置。图4显示了由于滤波电容放置位置不当产生的大电流环。

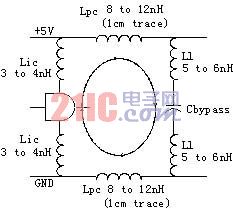

图5为电流环的模型。从电流环模型中我们可以看出,环路中存在寄生电感,它们在高频状态下表现为环路的阻抗可导致供给电源产生尖峰,并会辐射电磁波从而干扰系统的其他部分。环路中Ll为电容管脚引线的封装电感;Lpc为电容管脚到器件电源或者地管脚之间的PCB传输线的寄生电感;Lic为器件管脚引线的寄生电感。另外,在前面我们讨论过电容本身也是具有寄生电感ESL的。这样回路的总电感为:L=2Ll+ 2Lpc+2Lic+ESL。由于环路的寄生电感将会给整个系统带来电磁干扰,产生电压尖峰,这个电压尖峰值同串联电感之间存在一定的关系.

这里V为最大噪声电压尖峰值,△t为瞬态持续时间,△I为器件瞬态电流,△t、△I值可以从器件手册中查得。例如74HC的瞬态电流典型值Icc为20mA,输出信号从零上升到Icc或者从Icc下降到零需要的时间为4ns,如果现在我们试图控制感性噪声的尖峰在100mV以内,那么由上面的公式我们可以求得串联电感L的最大值不超过20nH。在PCB板设计时,设计者可以通过以下几种方式来降低回路电感:选择寄生电感比较小的电容,降低ESL(不同型号电容的寄生电感值见表1);尽量使用贴片电容以减小电容引线长,降低Ll值;合理的放置电容,使用电源层或地平面层代替电源或者地传输线,减小电源地传输线电感Lpc;合理选择集成器件的封装,以降低Lic值,比如对于器件ADV478来说,PLCC封装的寄生电感比DIP封装的寄生电感要小2nH到3nH。

4 电源扰动及地弹噪声的产生机理