识读解码控制系统电路图时,主要是识读解码CPU电路,其他各存储器可以作顺便识读解决。下面按照这个思路来识读该解码控制系统电路图。

1. 先看 CPU的基本电路

首先看电源供电电路。解码 CPU芯片 C1610 的④脚(VCC和 VCC1) 、22脚( VCC2) 、37脚( VCC3) 和64脚( VCC4) 都是 +5 V数字电源供电端,它的①脚(VSS1) 、21脚( VSS2) 、38脚(VSS3) 和63脚( VSS4) 都是接地端。而两个 EPROM芯片 27C040,其32脚(VCC) 和①脚( VPP) 都是由数字电源供电、而16脚(VSS)是接地端。还有两个 SRAM芯片 I DT71024,其32脚(VCC) 和30脚( A17) 都是接到 +5 V数字电源,16脚(GND)是接地端。

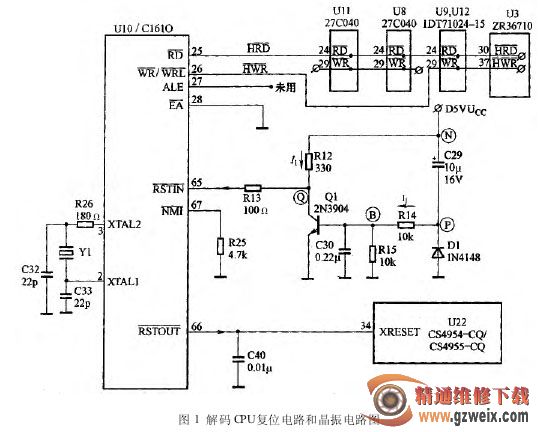

再看晶振电路。解码 CPU的晶振电路和复位电路画在一起,如图 1 所示。其中,芯片②脚(XTALl )、③脚( XTAL2) 内外电路组成 16 MHz 晶振电路,由晶振元件Y1、电阻 R26 和两电容 C32、C33 组成 16 MHz 振荡电路。两个电容是振荡负载电容。振荡电路输出 16 MHz振荡信号,可用来作解码 CPU的工作时钟和有关定时信号。

再看解码 CPU复位电路。该电路主要由 D1、Q1、C29、R12~R15 等组成。刚开机时,复位电容 C29 的电压不能突变,UP=UN,随着 C29 不断充电,其端电压 UC29:UN—UP也在逐渐增加,而且 UP随着 UN值上升而上升,UP经三极管 Q1 基极电阻 R14 加到其基极 b。在开始一段时间内,Q1 的导通程度很强,使“Q”点有一段时间的低电平,要求该低电平时间大于芯片的复位时间。C30是防止 Q1 发生寄生振荡。当 U

N值较稳定后,UP值进入逐渐下降阶段,Q1 的导通程度下降,最终截止。最后,“Q”点电压是经数字电源、R12 提供,电压升高且保持稳定状态。UQ经 R13 进入 C1610 的65脚(RSTIN),作为复位输入电压对芯片内电路完成复位。C161066脚(RSTOUT) 输出复位信号,用来控制 TV编码器CS4954CQ/CS4955CQ的复位,该脚外接电容是滤波电容。

当关机时,UN电压下降,利用二极管 D1 电流的单向导电性,P点电压出现负值后又继续上升。D1 起下限钳位作用,使 UP电位不能低于-0. 7 V。R15 是分压保护电阻。

2. 再看 C1610 的几个接口控制电路

C1610 设置有 7 个接口电路,分别完成不同的控制功能。下面分别讨论各接口电路的控制功能。在讨论各控制功能时,读者应当细心、耐心地寻找各接口外部的电路,并分别画出各控制支路的电路图。

( 1) 识读解码 CPU接口 0 电路该芯片接口 0 电路的引出脚包括29~36脚(POLO~POL7) 和39~46脚( POHO~POH7) ,它们分别对应低 8 位和高 8 位数据线。经外部 I2C总线,它们与 U8和 U1l ( 27C040) ;U9 和U12(I DT71024—15) 和U3( 2R36710) 相应引出脚连接在一起。在不同模式下,这些引出脚的用途不同。该接口在多路I2C总线模式下,可用作地址 A线,或者地址/数据 A线;在多路信号分离 I2C 总线模式,可用作数据 I2C 总线。在多路信号分离总线模式下,29~36脚 (POLO~POL7) 在 8 位和 16 位数据时,都是作为 AD码( ADO~AD7) ;而39~46脚(PCHD-PCH7)在8位数据时作为地址A码(A8-A15),在16位时作为地址 / 数据 AD码(AD8~ADl 5)。经过整理,可以画出接口 0 电路。