2基于IEEE 1149.7标准的边界扫描测试系统设计

在具有TAP. 7接口的被测电路系统中进行边界扫描测试,需要满足两项条件:首先,被测系统的设计需符合IEEE 1149.7标准的规范;其次,需要有紧凑型边界扫描测试系统的支持。虽然标准提出了测试系统的功能要求,但对测试系统的构建方式与实现途径没有制定相应的规范。在深入研究IEEE 1149.7标准的结构与规范后,确定紧凑型边界扫描测试系统的设计方法。

2.1系统功能总体设计

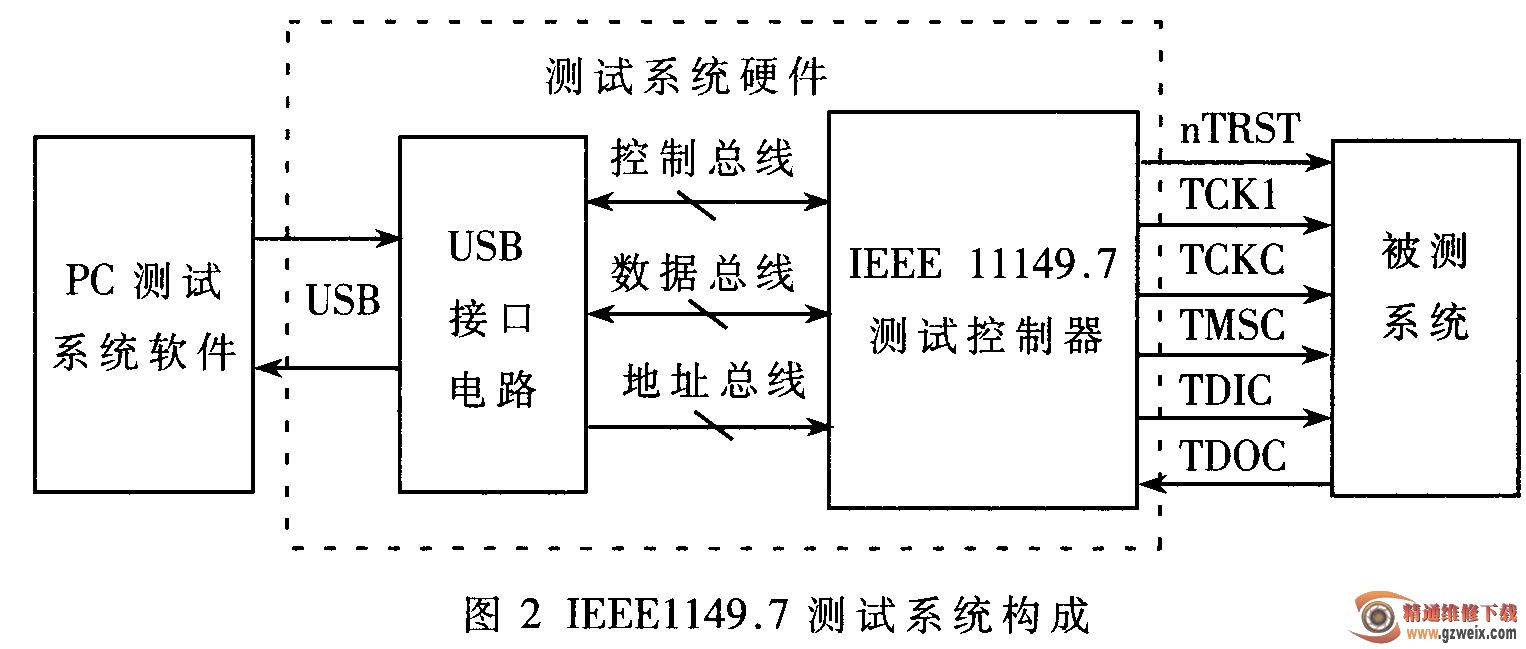

CJTAG测试体系包括测试软件和硬件平台,如图2所示。测试系统硬件包括两大功能模块:边界扫描测试控制器和USB接口电路,其中测试

控制器将PC机并行发送的测试信号转化为满足IEEE 1149.7标准的串行测试信号,在系统软件控制下进行扫描测试操作。

USB接口电路负责测试数据的交换及对测试控制器的管理。

系统软件功能:提取被测电路的信息;根据提取的信息产生测试矢量发送至硬件平台,并对响应数据进行分析与故障诊断等。即在PC上完成测试的设置、测试矢量的生成、测试数据的发送、响应数据的接收、响应数据的分析、测试结果的存储及测试控制器的USB驱动。

2.2测试系统硬件设计

CJTAG测试控制器作为测试体系最核心的部分,实际上是一种智能化的并行到串行的协议转换器:将PC机并行发送的测试数据或测试指令转化为待测芯片识别的串行CJTAG测试信号,且将待测芯片串行发送的响应数据并行发送至PC机。具体完成的工作:

(1)根据PC机的设置产生CJTAG测试时钟。

(2)读取PC机中的测试数据,并将这些并行的测试数据转化为串行的CJTAG测试信号。当无测试数据时,停止读取PC机的测试数据。

(3)采集待测芯片返回的响应数据,并将这些串行的响应数据并行写入PC机。当无响应数据时,停止采集响应数据。

2.2.1控制器总体设计

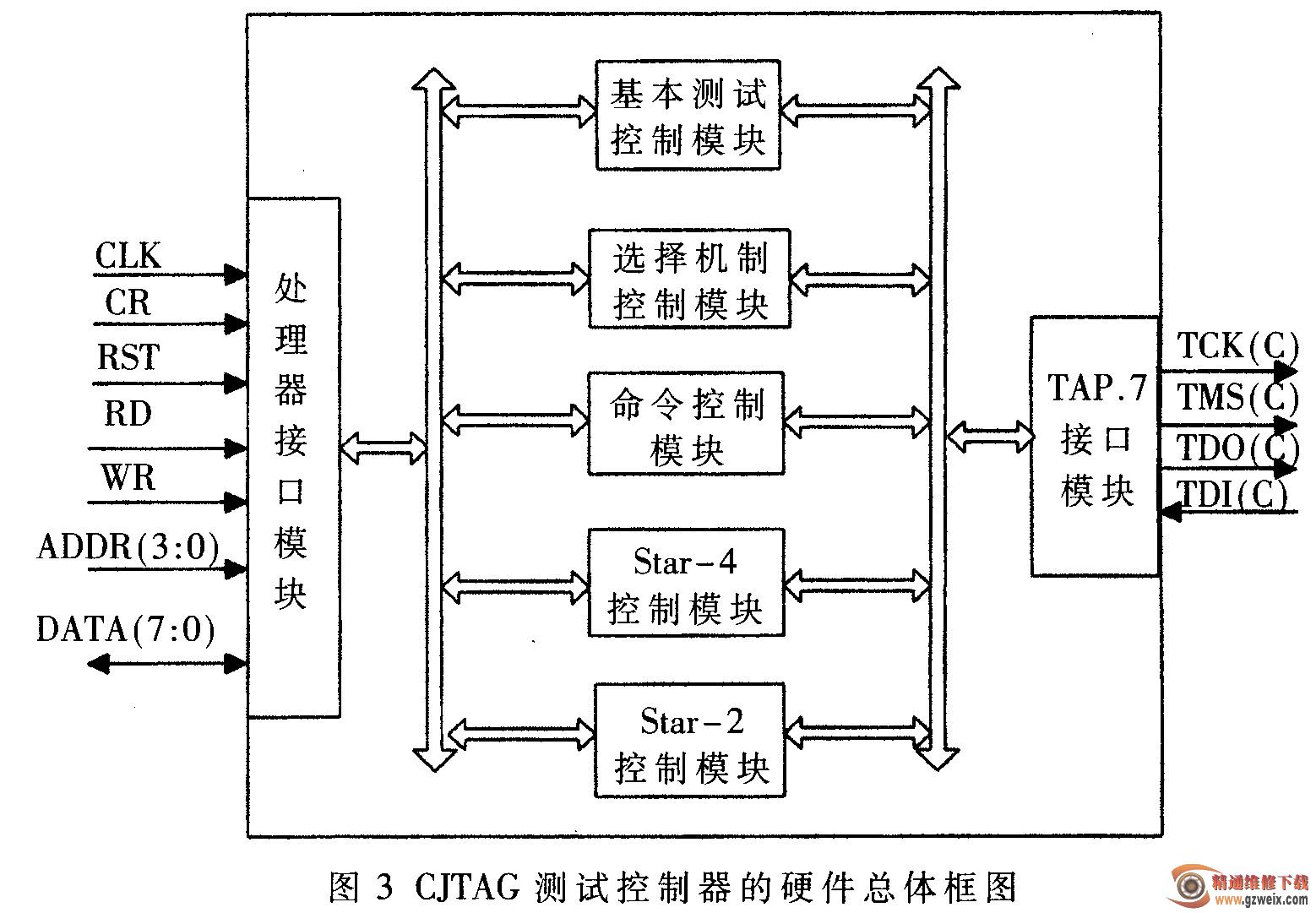

根据CJTAG测试控制器的功能需求,将此控制器的设计分为五个子模块和一个顶层模块。五个子模块分别为基本测试控制模块、选择机制控制模块、命令控制模块、Star - 4控制模块和Star - 2控制模块,分别实现了CJTAG的T0,T1 ,T3和T4层的功能。顶层模块包括处理器接口模块和TAP. 7接口模块,作为该控制器连接PC机和待测芯片的桥梁。具体硬件总体框图如图3所示。

2.2.2基本测试控制模块设计

基本测试控制模块实现T0层的串行扫描测试,以TAP. 7控制器状态机为基础设计一个模块状态机,产生串行扫描所需要的测试信号实时控制待测芯片。

此模块的工作过程:首先PC机将并行发送的测试数据和测试指令存储在该模块的数据存储器中。其次通过TMS引脚控制TAP. 7控制器进入Shift -xR状态且自循环,测试数据或测试指令通过TDO引脚串行发送至待测芯片中,同时响应数据通过TDI引脚由待测芯片串行传输到该模块的数据存储器中,最后将响应数据并行输出至PC机。