・上一文章:基于CC2530的脉搏感知节点设计

・下一文章:详解有线电视技术

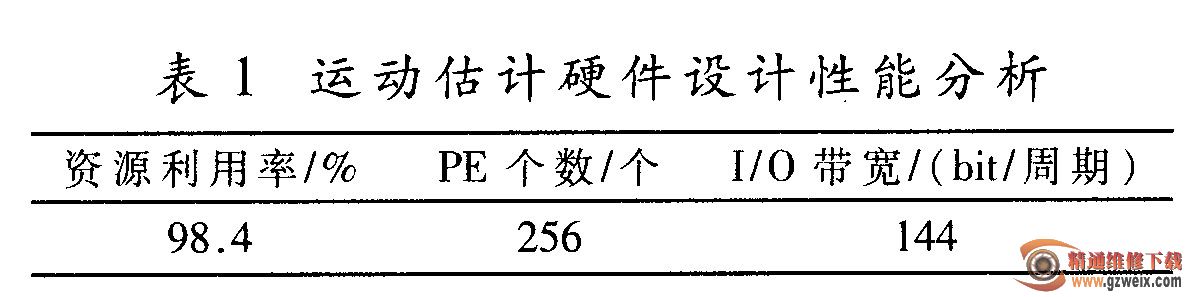

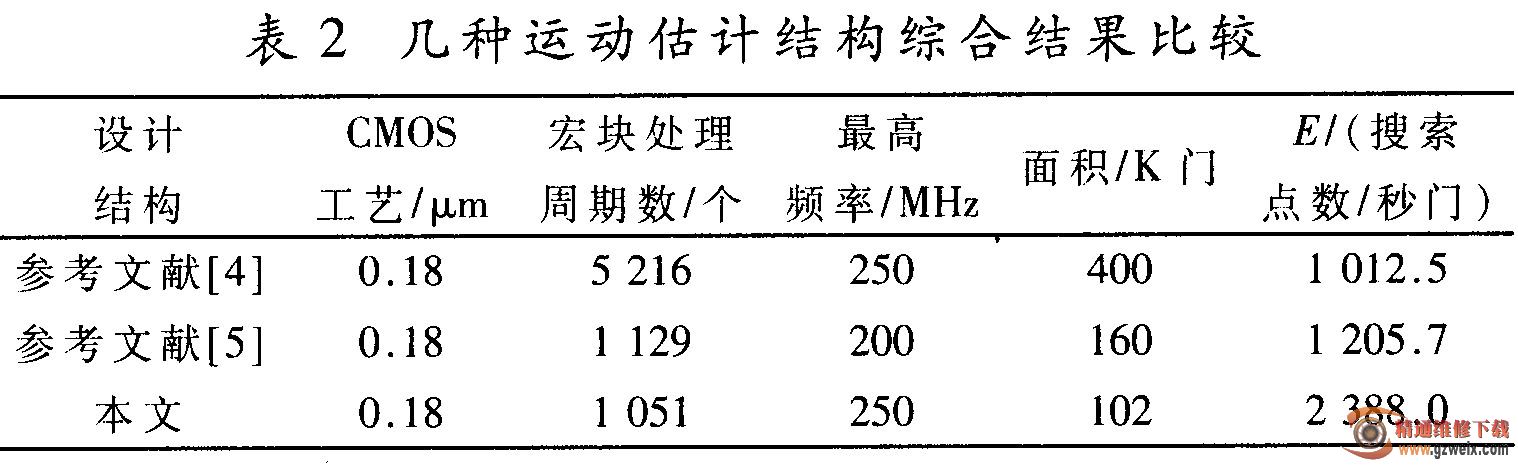

本文提出了一种适用于AVS的高性能整像素运动估计硬件设计,使用了Verilog HDL语言进行RTL级描述,用AVS软件RM5与的C程序产生测试码流,应用了Modelsim 6.5c仿真平台进行了逻辑功能的仿真验证。采用Synopsys的Design Compiler在SMIC 0.18 μm CMOS工艺库下综合,在最大频率为250 MHz时,门数为102 K(未包括存储器面积)。表1给出了运动估计硬件设计性能分析,这表明本文所设计的结构具有高性能、低带宽的优势。表2将本文提出的结构与其他几种运动估计结构进行了比较,其中引用了效率E作为一个重要的比较参数,E为结构每秒处理的搜索点数和实际面积的比值,具体公式见参考文献[5]。通过比较可以看出,本设计与参考文献[5]的设计均可实现对高清图像的实时处理,但本设计的最快时钟频率提升了25,面积减小了36.2%,效率提高了98%。

本文针对AVS视频标准,提出了一种适用于AVS的高性能整像素运动估计硬件设计。采用二维内置SAD加法树计算阵列,通过合理的安排片上存储,优化了加法器设计,大大提高了结构的性能。实验结果表明,本设计电路规模为102 K门,处理一个宏块只需要1 051个时钟周期,能够以2 388.0搜索点数/秒门的效率对高清图像进行运动估计。与同类设计相比,本设计具有电路规模小、处理速度快、I/0带宽低等优势。另外,本设计还可以作为IP核嵌人到特定的处理器中,对AVS高清视频进行实时处理。