2优化的解决方案

为了解决硬件和软件面临的设计难题,本文从硬件架构人手,借助于CPLD或FPGA芯片,辅以高效的软件设计,开发出了一套行之有效的解决方案。

2.1硬件设计

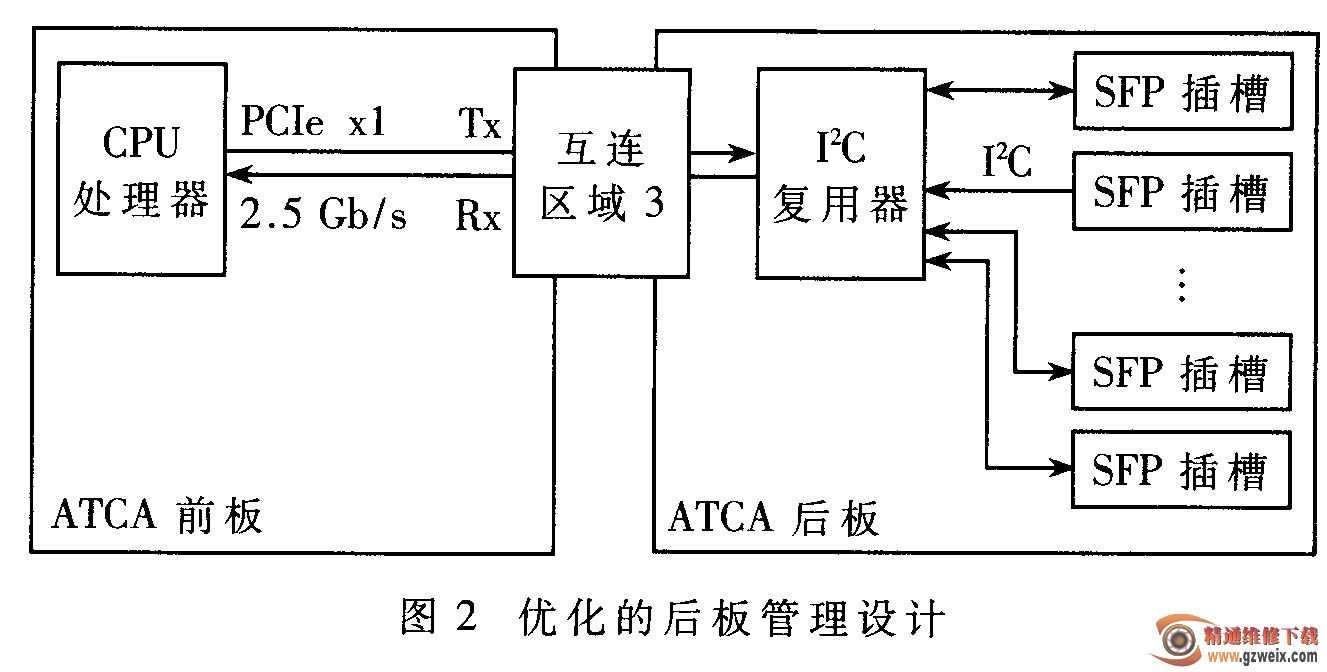

为了减少I℃接口所占用的前后板互连引脚数目,本文将执行I2C复用功能的芯片放到了后板上,这样只有一条I2C总线通过互连区域3(即只占用2根互连引脚),极大地节省了互连引脚的数目。另一方面,I2C复用器不采用商业专用芯片,而是采用CPLD或者FPGA,可为软件设计提供较佳的灵活性(如提供中断机制)。在本设计中,采用了FPGA 。

假设后板上安放了8个SFP插槽,与优化前的设计相比,优化后的设计节省了14个互连引脚。为了进一步提升处理器访问后板SFP模块的速率,本文用PCIe总线取代I2C总线,如图2所示。连接FPGA和处理器,PCIe总线占用4根互连引脚,虽然比12C总线多占2个引脚,但是速率提升到了2.5 Gb/s,远高于I℃的速率,使处理器和I2C复用器之间的速率瓶颈问题得以解决。选择PCIe的另一个好处是:如果采用中断方式,则PCIe不需要专用的中断引脚,因为它是依赖带内消息中断的。此外,连接FPGA和8个SFP插槽的8组I2C总线互相独立,所以FPGA可以并行地访问8个SFP模块,比串行访问的效率提升了8倍。

2.2软件设计

如何处理高速处理器与低速外围总线之间的关系,是软件设计的主要任务。处理器的速度一般在几百到上千兆赫兹,而I2C总线的速度一般最高为400 kHz(普通的只有100 kHz),两者完全不在一个数量级上。所以,FPGA不但要承担扩展I2C总线的任务,而且要承担管理低速总线设备的任务,使处理器有更多的时间处理计算量大、优先级高的任务。因此,软件设计的主要工作在FPGA上。

FPGA中集成了2个成熟的IP核:一个是PCIe内核,工作于从设备(End Point)模式,1路通道(x1 Lane);另一个是I2C内核,工作于主设备(Maste动模式,各条总线互相独立。FPGA软件的设计需要考虑两方面的因素:一是高效,尽可能降低CPU的负担;二是支持热插拔,因为SFP模块随时都可能被插人或拔出,导致I2C总线上正在运行的协议随时会被中断而产生异常。

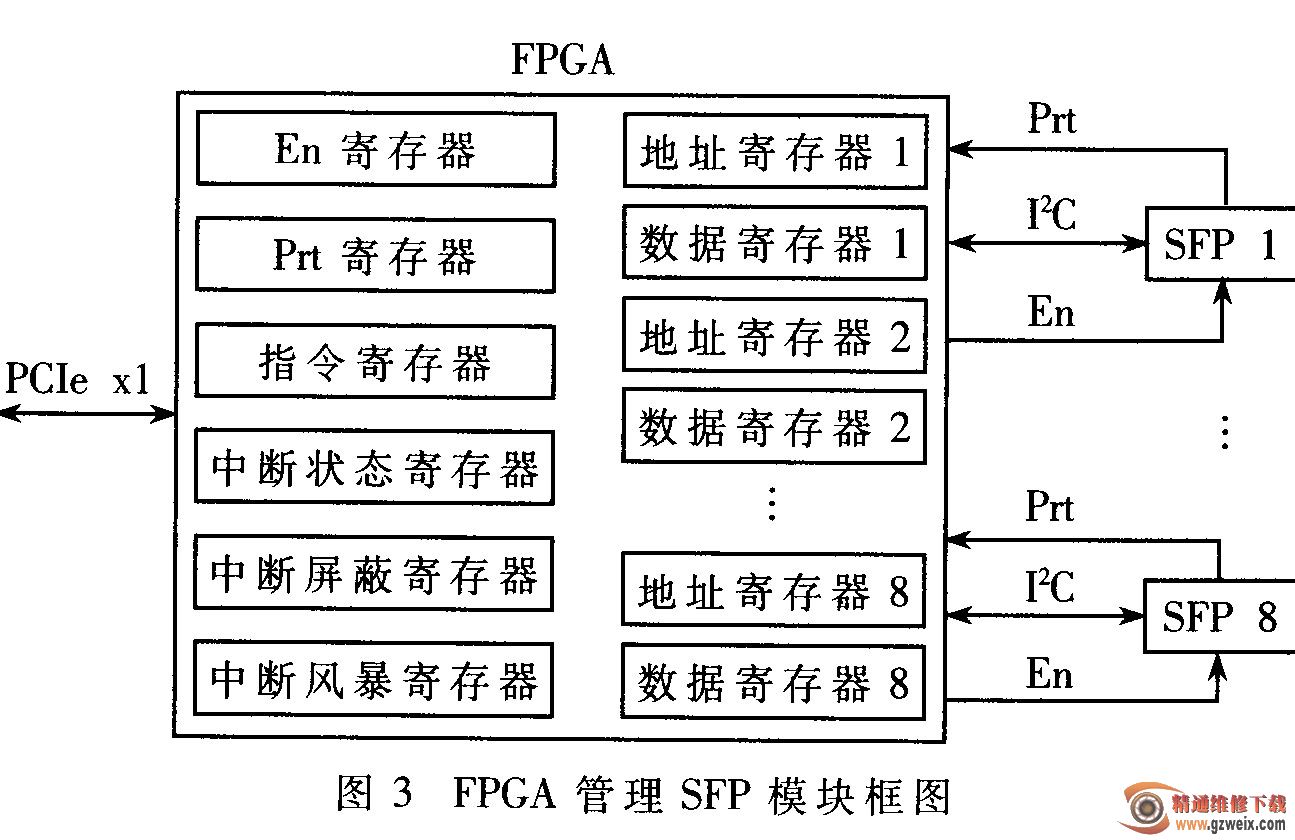

FPGA中的寄存器设计以及与SFP模块之间的控制连线如图3所示。根据SFP标准,每个模块会引出一个存在(Prt)信号和一个使能(En)信号,FPGA中的使能(En)寄存器通过使能信号控制每个模块是否工作。存在(Prt)寄存器通过读取存在信号反映每个SFP插槽中是否插入了SFP模块。重启寄存器用于重启各条I2C总线,特别是当I2C协议正在总线上运行时,模块被突然拔出,I2C总线因为缺少客户端的响应而产生异常,此时会在中断状态寄存器反映异常情况,并且自动重启I2C总线,以便下次模块插人时可以正常工作。CPU也可以主动设置指令寄存器来重启某条I2总线。